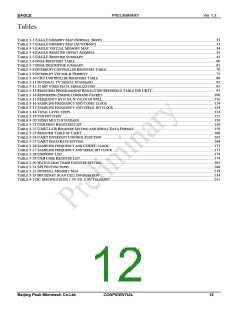

EAGLE

PRELIMINARY

Ver 1.3

3.24.4 PWM.................................................................................................................................................................... 184

3.24.5 Capture Mode...................................................................................................................................................... 185

3.24.6 Timer Registers ................................................................................................................................................... 186

3.24.6.1 Timer Clock Selection Register (TCSR0 / TCSR1 / TCSR2 / TCSR3) .............................................................................186

3.24.6.2 Timer Control Register (TCON0 / TCON1 / TCON2 / TCON3).......................................................................................186

3.24.6.3 Timer Counter / Output Period Register (TCNT0 / TCNT1 / TCNT2 / TCNT3)...............................................................187

3.24.6.4 Capture Counter / PWM Duty Compare Register (TDUT0 / TDUT1 / TDUT2 / TDUT3) ...............................................187

3.24.6.5 Output Pulse Count Register (TPUL0 / TPUL1 / TPUL2 / TPUL3)..................................................................................187

3.24.7 Interrupts............................................................................................................................................................. 187

3.25 GPIO ........................................................................................................................................................................... 188

3.25.1 Features .............................................................................................................................................................. 188

3.25.2 Register Map....................................................................................................................................................... 188

3.25.2.1 Port Direction Register (PxDIR)........................................................................................................................................188

3.25.2.2 Port Direction Output Mode Register (PxOUT).................................................................................................................188

3.25.2.3 Port Direction Input Mode Register (PxIN) ......................................................................................................................188

3.25.2.4 Port Output Data Level Register (PxOLEV)......................................................................................................................189

3.25.2.5 Port Output Data High Level Setting Register (PxOH)......................................................................................................189

3.25.2.6 Port Output Data Low Level Setting Register (PxOL).......................................................................................................189

3.25.2.7 Port Input Data Level Register (PxILEV)..........................................................................................................................189

3.25.3 Mapping .............................................................................................................................................................. 190

3.26 REAL TIME CLOCK....................................................................................................................................................... 191

3.26.1 RTC Control Register (RTCCON)....................................................................................................................... 191

3.26.2 SEC Register (RTCSEC) ..................................................................................................................................... 191

3.26.3 MIN Register (RTCMIN)..................................................................................................................................... 191

3.26.4 HOUR Register (RTCHOUR) ............................................................................................................................. 191

3.26.5 DAY Register (RTCDAY) .................................................................................................................................... 192

3.26.6 WEEK Register (RTCWEEK).............................................................................................................................. 192

3.26.7 MONTH Register (RTCMON)............................................................................................................................. 192

3.26.8 YEAR Register (RTCYEAR)................................................................................................................................. 192

3.27 TWI CONTROLLER....................................................................................................................................................... 193

3.27.1 Features .............................................................................................................................................................. 193

3.27.2 TWI Controller Block Diagram........................................................................................................................... 193

3.27.3 DATA TRANSFER FORMAT.............................................................................................................................. 194

3.27.4 START AND STOP CONDITION........................................................................................................................ 194

3.27.5 ACK SIGNAL TRANSMISSION .......................................................................................................................... 195

3.27.6 READ-WRITE OPERATION............................................................................................................................... 195

3.27.7 BUS ARBITRATION PROCEDURES ................................................................................................................. 195

3.27.8 ABORT CONDITION.......................................................................................................................................... 196

3.27.9 Operational Flow Diagrams ............................................................................................................................... 197

3.27.9.1 TWI initialization...............................................................................................................................................................197

3.27.9.2 TWI Transmit/Receive Flow chart.....................................................................................................................................198

3.27.10

TWI Registers.................................................................................................................................................. 202

TWI Control Register (TWICON).................................................................................................................................202

TWI Status Register (TWISTAT)..................................................................................................................................203

TWI Address Register(TWIADDR) ..............................................................................................................................204

TWI Data Register ( TWIDATA)..................................................................................................................................204

TWI Baud-rate 0 Register (TWIBR0 ) ..........................................................................................................................204

TWI Baud-rate 1 Register (TWIBR1) ...........................................................................................................................204

3.27.10.1

3.27.10.2

3.27.10.3

3.27.10.4

3.27.10.5

3.27.10.6

3.28 SPI(SERIAL PERIPHERAL INTERFACE).......................................................................................................................... 205

3.28.1 Features .............................................................................................................................................................. 205

3.28.2 SPI Block Diagram.............................................................................................................................................. 205

3.28.3 SPI Pins............................................................................................................................................................... 206

3.28.4 SPI Operating Modes.......................................................................................................................................... 206

3.28.4.1

3.28.4.2

Master Mode ................................................................................................................................................... 206

Slave Mode...................................................................................................................................................... 206

3.28.5 SCK Phase and Polarity Control ........................................................................................................................ 207

3.28.6 Data Transfer Timing.......................................................................................................................................... 207

3.28.7 SPI Register Description..................................................................................................................................... 208

3.28.7.1 SPI Control Register (SPICON)........................................................................................................................................208

3.28.7.2 SPI Baud Rate Register (SPIBR) .......................................................................................................................................209

3.28.7.3 SPI Status Register (SPISTAT)..........................................................................................................................................209

3.28.7.4 SPI Data Register (SPID)...................................................................................................................................................210

3.28.7.5 SPI SSX Control Register (SPISCON) ..............................................................................................................................210

3.28.7.6 SPI Interrupt Mask Register (SPIIM).................................................................................................................................210

3.28.7.7 SPI Transfer Mode Register (SPITM)................................................................................................................................211

Beijing Peak Microtech Co.Ltd.

CONFIDENTIAL

8

ETC [ ETC ]

ETC [ ETC ]