EAGLE

PRELIMINARY

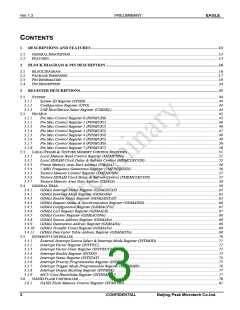

Ver 1.3

3.6.2

3.6.3

3.6.4

3.6.5

3.6.6

3.6.7

3.6.8

3.6.9

NAND Flash Memory Command Set Register (NFMCMD).................................................................................. 82

NAND Flash Memory Address Register (NFMADDR) ......................................................................................... 82

NAND Flash Memory Data Register (NFMDATA)............................................................................................... 82

NAND Flash Memory DMA Data Register (NFMDMA) ...................................................................................... 82

NAND Flash Memory Direct Read Destination Address Register (NFMDIR) ..................................................... 82

NAND Flash Memory Operation Status Register (NFMSTAT)............................................................................. 83

NAND Flash Memory Low / High Start Address Register (NFMLSM / NFMHSM)............................................. 83

NAND Flash Memory ECC(Error Correction Code) Register(NFMECC)........................................................... 83

3.6.10 NAND Flash Memory ECC Code for LSN data (NFMECCL) .............................................................................. 84

3.6.11 NAND Flash Memory Configuration Register (NFMCFG).................................................................................. 84

3.7

CRT CONTROLLER ........................................................................................................................................................ 85

CRT Base Address Register(CRTBA).................................................................................................................... 86

CRT Horizontal Total Register(CRTHT)............................................................................................................... 86

CRT Horizontal Sync. Start / End Register(CRTHS) ............................................................................................ 86

CRT Horizontal Active Start / End Register(CRTHA)........................................................................................... 87

CRT Vertical Total Register(CRTVT) ................................................................................................................... 87

CRT Vertical Sync. Start / End Register(CRTVS) ................................................................................................. 87

CRT Vertical Active Start / End Register(CRTVA) ............................................................................................... 87

CRT Display Current X / Y Position Register(CRTXY)......................................................................................... 88

CRT Status Register(CRTSTAT)............................................................................................................................ 88

3.7.1

3.7.2

3.7.3

3.7.4

3.7.5

3.7.6

3.7.7

3.7.8

3.7.9

3.7.10 CRT Control Register(CRTCON).......................................................................................................................... 89

3.7.11 CRT Overlay & DAC Control Register(CRTOEDAC).......................................................................................... 91

3.7.12 CRT VESA Power Management Control Register(CRTPM)................................................................................. 91

3.8

GRAPHIC CONTROLLER.................................................................................................................................................. 98

Packet Write Pointer Register (GRAPWP) ........................................................................................................... 98

Packet Read Pointer Register (GRAPRP)............................................................................................................. 98

Rendering Control Register (GRARCON)............................................................................................................. 98

Current Display Bank Register (GRACDB).......................................................................................................... 99

Flip Command Count Register (GRAFCC)........................................................................................................... 99

Non-Texture Memory Mode Register (GRANONTEXTURE)................................................................................ 99

H.264 DECODER .......................................................................................................................................................... 101

Features .............................................................................................................................................................. 101

Block Diagram .................................................................................................................................................... 101

Decoding Operation Related Registers............................................................................................................... 101

3.8.1

3.8.2

3.8.3

3.8.4

3.8.5

3.8.6

3.9

3.9.1

3.9.2

3.9.3

3.9.3.1

3.9.3.2

Decoder Enable Register (H264DON)...............................................................................................................................101

Decoder Mode Register (H264DECMODE)......................................................................................................................101

Decoder Endian Register (H264ENDIAN) ........................................................................................................................102

Error Detection Register (H264ERRON)...........................................................................................................................102

Bit-stream Buffer Start Address Register (H264BSA).......................................................................................................102

Bit-stream Buffer End Address Register (H264BEA)........................................................................................................102

Bit-stream Buffer Read Address Register (H264BRA)......................................................................................................102

Bit-stream Buffer New Read Address Register (H264BRAW)..........................................................................................103

Decoded Image Related Registers....................................................................................................................... 103

Y0 Frame Buffer Start Address Register (H264Y0SA) .....................................................................................................103

Y1 Frame Buffer Start Address Register (H264Y1SA) .....................................................................................................103

Y2 Frame Buffer Start Address Register (H264Y2SA) .....................................................................................................103

C0 Frame Buffer Start Address Register (H264C0SA)......................................................................................................103

C1 Frame Buffer Start Address Register (H264C1SA)......................................................................................................104

C2 Frame Buffer Start Address Register (H264C2SA)......................................................................................................104

Horizontal Size of Decoded Image 0 Register (H264F0MXS) ..........................................................................................104

Vertical Size of Decoded Image 0 Register (H264F0MYS) ..............................................................................................104

Horizontal Size of Decoded Image 1 Register (H264F1MXS) ..........................................................................................104

3.9.3.3

3.9.3.4

3.9.3.5

3.9.3.6

3.9.3.7

3.9.3.8

3.9.4

3.9.4.1

3.9.4.2

3.9.4.3

3.9.4.4

3.9.4.5

3.9.4.6

3.9.4.7

3.9.4.8

3.9.4.9

3.9.4.10 Vertical Size of Decoded Image 1 Register (H264F1MYS) ..............................................................................................105

3.9.4.11 Horizontal Size of Decoded Image 2 Register (H264F2MXS) ..........................................................................................105

3.9.4.12 Vertical Size of Decoded Image 2 Register (H264F2MYS) ..............................................................................................105

3.9.4.13 Horizontal Size of Scaler Output Register (H264XOUTP)................................................................................................105

3.9.4.14 Vertical Size of Scaler Output Register (H264YOUTP)....................................................................................................105

3.9.4.15 Decoder Frame Buffer Pointer Register (H264FP) ............................................................................................................106

3.9.4.16 Scaler Frame Buffer Pointer Register (H264SP)................................................................................................................106

3.9.4.17 Scaler Enable Register (H264SON)...................................................................................................................................106

3.9.4.18 Scaler Endian Register (H264SWAP)................................................................................................................................106

3.9.5

Decoding Interrupt Related Registers................................................................................................................. 106

Interrupt Enable Register (H264INT) ................................................................................................................................106

Interrupt Flag Register (H264FLAG).................................................................................................................................107

Interrupt Half Address Register (H264IHA)......................................................................................................................107

3.9.5.1

3.9.5.2

3.9.5.3

Beijing Peak Microtech Co.Ltd.

CONFIDENTIAL

4

ETC [ ETC ]

ETC [ ETC ]