Ver 1.3

PRELIMINARY

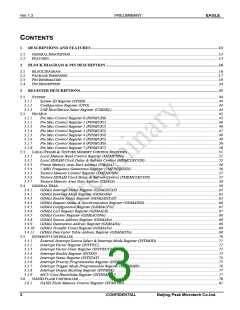

EAGLE

3.9.5.4

3.9.6

3.9.7

Interrupt End Address Register (H264IEA) .......................................................................................................................107

Decoded Image Data Path...................................................................................................................................107

H/W Simulation Method ......................................................................................................................................108

3.10 PLL & POWER MANAGER ............................................................................................................................................109

3.10.1 System Clock Source Select Register (SPLLCKSEL)...........................................................................................109

3.10.2 System PLL Control Register (SPLLCON)..........................................................................................................109

3.10.3 System PLL Program Register (SPLLPMN)........................................................................................................110

3.10.4 CRT Clock Source Select Register (CPLLCKSEL)..............................................................................................111

3.10.5 CRT PLL Control Register (CPLLCON).............................................................................................................111

3.10.6 CRT PLL Program Register (CPLLPMN)...........................................................................................................111

3.10.7 USB Clock Source Select Register (UPLLCKSEL)..............................................................................................111

3.10.8 USB PLL Control Register (UPLLCON).............................................................................................................112

3.10.9 USB PLL Program Register (UPLLPMN)...........................................................................................................112

3.10.10

H264/MJPEG Clock Enable bit Register (HMCLKEN)..................................................................................112

3.11 SD CARD CONTROLLER ...............................................................................................................................................113

3.11.1 Features...............................................................................................................................................................113

3.11.2 Block Diagram.....................................................................................................................................................113

3.11.3 SD Bus Protocol ..................................................................................................................................................113

3.11.3.1 No Response and No Data Operations ...............................................................................................................................114

3.11.3.2 Data Read Operation..........................................................................................................................................................114

3.11.3.3 Data Write Operation .........................................................................................................................................................114

3.11.4.1 SDC Control Register (SDCCON).....................................................................................................................................115

3.11.4.2 SDC Status Register (SDCSTAT)......................................................................................................................................115

3.11.4.3 SDC Clock Divide Register (SDCCD)...............................................................................................................................116

3.11.4.4 SDC Response Time Out Register (SDCRTO)..................................................................................................................117

3.11.4.5 SDC Read Data Time Out Register (SDCRDTO)..............................................................................................................117

3.11.4.6 SDC Block Length Register (SDCBL)...............................................................................................................................117

3.11.4.7 SDC Number of Block Register (SDCNOB) .....................................................................................................................117

3.11.4.8 SDC Interrupt Enable Register (SDCIE)............................................................................................................................117

3.11.4.9 SDC Command Control Register (SDCCMDCON)...........................................................................................................118

3.11.4.10

3.11.4.11

3.11.4.12

SDC Command Argument Register (SDCCMDA)........................................................................................................119

SDC Response FIFO Access Register (SDCRFA) ........................................................................................................119

SDC Data FIFO Access Register (SDCDFA)................................................................................................................119

3.12 SOUND MIXER..............................................................................................................................................................120

3.12.1 Features...............................................................................................................................................................120

3.12.2 Block Diagram.....................................................................................................................................................120

3.12.3 Channel Register Map.........................................................................................................................................121

3.12.3.1 Sound Data Channel n Control Register (SNDCONn).......................................................................................................121

3.12.3.2 Sound Data Channel n Start Address Set Register (SNDADRn)........................................................................................121

3.12.3.3 Sound Data Channel n Size Set Register (SNDSIZn) ........................................................................................................122

3.12.3.4 Sound Data Channel On / Status Register (SNDCHON) ...................................................................................................122

3.12.3.5 Sound Data Channel Interrupt Status Register (SNDIRQSTAT)........................................................................................122

3.12.4 Status and Playback Set Register Map ................................................................................................................123

3.12.4.1 Sound Mixer Playback Set Register (SNDPLAY) .............................................................................................................123

3.12.5 Test Mode Register Map......................................................................................................................................123

3.12.5.1 Sound Data Channel n FIFO Buffer Register (SNDBUFn)................................................................................................123

3.12.5.2 Sound Data Channel n FIFO Level Status Register (SNDLEVn) ......................................................................................123

3.12.6 Audio Serial Interface Format.............................................................................................................................124

3.12.6.1 MSB (Left)-justified format ...............................................................................................................................................124

3.12.6.2 Codec clock and Serial bit clock frequency .......................................................................................................................124

3.12.6.3 Volume and Balance Control .............................................................................................................................................124

3.13 VIDEO ENCODER ..........................................................................................................................................................126

3.13.1 Multi-Standard.....................................................................................................................................................126

3.13.2 Features...............................................................................................................................................................126

3.13.3 General Description ............................................................................................................................................127

3.13.4 Control Registers.................................................................................................................................................132

3.13.5 Enc_Mode Register (ENCMODE).......................................................................................................................132

3.13.6 Enc_Hue Adjust Register (ENCHUE) .................................................................................................................133

3.13.7 Enc_VPC Register (ENCVPC) ............................................................................................................................133

3.13.8 Enc_HPC Register (ENCHPC) ...........................................................................................................................133

3.13.9 Enc_Test Register (ENCTEST)............................................................................................................................134

3.13.10

3.13.11

3.13.12

Enc_Brightness Register (ENCBRIGHT) ........................................................................................................134

Enc_Contrast Register (ENCCONTRAST)......................................................................................................134

Enc_Saturation Register (ENCSATURATION)...............................................................................................134

3.14 CSC IMAGE CAPTURER ................................................................................................................................................136

5

CONFIDENTIAL Beijing Peak Microtech Co.Ltd.

ETC [ ETC ]

ETC [ ETC ]