EAGLE

PRELIMINARY

Ver 1.3

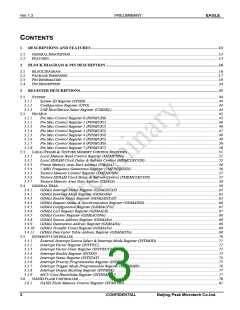

3.14.1 Description.......................................................................................................................................................... 136

3.14.2 Features .............................................................................................................................................................. 136

3.14.3 Block Diagram .................................................................................................................................................... 136

3.14.4 Operational Descriptions.................................................................................................................................... 137

3.14.5 Engine Control Register (CSCICCON)............................................................................................................... 137

3.14.6 Pixel Gain Control Register (CSCICPGCON).................................................................................................... 139

3.14.7 X Coordinate Down Scaling Control Register (CSCICXDSCON)...................................................................... 139

3.14.8 Y Coordinate Down Scaling Control Register (CSCICYDSCON) ...................................................................... 140

3.14.9 Rendering X Start Point Register (CSCICXSP) .................................................................................................. 140

3.14.10

Rendering Y Start Point Register (CSCICYSP)............................................................................................... 140

3.15 OSD CONTROLLER ...................................................................................................................................................... 141

3.15.1 Features .............................................................................................................................................................. 141

3.15.2 Block Diagram .................................................................................................................................................... 141

3.15.3 OSD Control Register (OSDCON)...................................................................................................................... 142

3.15.4 OSD Transparent Color Register (OSDTC)........................................................................................................ 142

3.15.5 Alpha Blending Control Register (OSDACON) .................................................................................................. 142

3.15.6 OSD Alpha Blending Color Register 0 (OSDAC0) ............................................................................................. 143

3.15.7 OSD Alpha Blending Color Register 1 (OSDAC1) ............................................................................................. 143

3.15.8 OSD Alpha Blending Color Register 2 (OSDAC2) ............................................................................................. 143

3.15.9 OSD Alpha Blending Color Register 3 (OSDAC3) ............................................................................................. 143

3.15.10

3.15.11

3.15.12

3.15.13

3.15.14

3.15.15

OSD Frame Memory Start Address Register (OSDFMSA)............................................................................. 143

Palette RAM Data Register (OSDPRD).......................................................................................................... 144

First OSD window start position Register (OSDWSP0).................................................................................. 144

First OSD window size Register (OSDWS0)................................................................................................... 144

Second OSD window start position Register (OSDWSP1).............................................................................. 145

Second OSD window size Register (OSDWS1) ............................................................................................... 145

3.16 JPEG IMAGE CAPTURER .............................................................................................................................................. 146

3.16.1 Description.......................................................................................................................................................... 146

3.16.2 Features .............................................................................................................................................................. 146

3.16.3 Block Diagram .................................................................................................................................................... 146

3.16.4 Operational Descriptions.................................................................................................................................... 147

3.16.5 Engine Control Register (JICCON) .................................................................................................................... 147

3.16.6 Pixel Gain Control Register (JICPGCON)......................................................................................................... 148

3.16.7 Rendering X Start Point Register (JICXSP)........................................................................................................ 148

3.16.8 Rendering Y Start Point Register (JICYSP) ........................................................................................................ 149

3.16.9 Rendering Base Start Address Register (JICBSA) .............................................................................................. 149

3.16.10

3.16.11

Rendering Status Register (JICSTAT)............................................................................................................. 149

Rendering Y Offset Address Register (JICYOFFA)......................................................................................... 149

3.17 USB HOST CONTROLLER............................................................................................................................................. 150

3.17.1 Host Controller Features .................................................................................................................................... 150

3.17.2 Host Controller Operational Registers ............................................................................................................... 150

3.18 YC IMAGE CAPTURER.................................................................................................................................................. 151

3.18.1 Description.......................................................................................................................................................... 151

3.18.2 Features .............................................................................................................................................................. 151

3.18.3 Block Diagram .................................................................................................................................................... 151

3.18.4 Operational Descriptions.................................................................................................................................... 152

3.18.5 Engine Control Register (YCICCON) ................................................................................................................. 152

3.18.6 Y Buffer 0 Start Address Register (YCICYB0SA) ................................................................................................ 153

3.18.7 Y Buffer 1 Start Address Register (YCICYB1SA) ................................................................................................ 153

3.18.8 Y Buffer 2 Start Address Register (YCICYB2SA) ................................................................................................ 153

3.18.9 C Buffer 0 Start Address Register (YCICCB0SA) ............................................................................................... 154

3.18.10

3.18.11

3.18.12

3.18.13

3.18.14

3.18.15

C Buffer 1 Start Address Register (YCICCB1SA) ........................................................................................... 154

C Buffer 2 Start Address Register (YCICCB2SA) ........................................................................................... 154

Input Source Image X Size Register (YCICISXS) ............................................................................................ 154

Input Source Image Y Size Register (YCICISYS)............................................................................................. 154

Output Image X Size Register (YCICOXS)...................................................................................................... 154

Output Image Y Size Register (YCICOYS) ...................................................................................................... 155

3.19 UART.......................................................................................................................................................................... 156

3.19.2 UART Channel 0~3 Receiver Buffer Register (URB0 ~ URB3).......................................................................... 160

3.19.3 UART Channel 0~3 Transmitter Holding Register (UTH0 ~ UTH3).................................................................. 160

3.19.4 UART Channel 0~3 Interrupt Enable Register (UIE0 ~ UIE3) .......................................................................... 161

3.19.5 UART Channel 0~3 Interrupt Identification Register (UII0 ~ UII3) .................................................................. 161

Beijing Peak Microtech Co.Ltd.

CONFIDENTIAL

6

ETC [ ETC ]

ETC [ ETC ]