Ver 1.3

PRELIMINARY

EAGLE

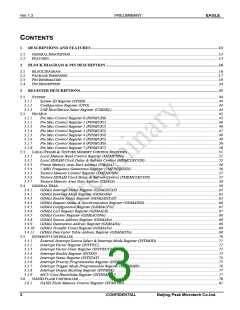

3.19.6 UART Channel 0~3 FIFO Control Register (UFCON0 ~ UFCON3) .................................................................162

3.19.7 UART Channel 0~3 Line Control Register (ULCON0 ~ULCON3).....................................................................162

3.19.8 UART Channel 0~3 Line Status Register (ULSTAT0 ~ ULSTAT3).....................................................................163

3.19.9 UART Channel 0~3 Divisor Latch LSB Register (UDLL0 ~ UDLL3).................................................................163

3.19.10

3.19.11

UART Channel 0~3 Divisor Latch MSB Register (UDLM0 ~ UDLM3) .........................................................163

Operation Sequence Flow................................................................................................................................164

3.20 KEY SCAN ....................................................................................................................................................................165

3.20.1 Description ..........................................................................................................................................................165

3.20.2 Features...............................................................................................................................................................165

3.20.3 Block Diagram.....................................................................................................................................................165

3.20.4 Operational Descriptions ....................................................................................................................................165

3.20.5 Key Scan Control Register (KSCON)..................................................................................................................166

3.20.6 Key Scan Counter Register (KSCNT)..................................................................................................................166

3.20.7 Key Scan Data Register 1 (KSD1).......................................................................................................................166

3.20.8 Key Scan Data Register 2 (KSD2).......................................................................................................................167

3.21 I2S WITH ADPCM .......................................................................................................................................................168

3.21.1 Features...............................................................................................................................................................168

3.21.2 Block Diagram.....................................................................................................................................................168

3.21.3 Register Map .......................................................................................................................................................169

3.21.3.1 I2S Control Register (I2SCON) .........................................................................................................................................169

3.21.3.2 I2S Mode Register (I2SMOD) ...........................................................................................................................................169

3.21.3.3 I2S Pre-scaler Register (I2SPS)..........................................................................................................................................170

3.21.3.4 I2S Status Register (I2SSTAT) ..........................................................................................................................................171

3.21.3.5 I2S Data Register (I2SDATA) ...........................................................................................................................................171

3.21.4 Example for Register Set .....................................................................................................................................172

3.21.4.1 To Start I2S operation.........................................................................................................................................................172

3.21.4.2 To End I2S operation..........................................................................................................................................................172

3.21.5 Audio Serial Interface Format.............................................................................................................................172

3.21.5.1 I2S-bus format....................................................................................................................................................................172

3.21.5.2 MSB(Left)-justified format................................................................................................................................................172

3.21.6 Sampling Frequency and Master Clock...............................................................................................................173

3.21.6.1 CODEC Clock....................................................................................................................................................................173

3.21.6.2 Serial bit clock frequency...................................................................................................................................................173

3.22 USB DEVICE ................................................................................................................................................................174

3.22.1 USB Register Summary........................................................................................................................................174

3.22.2 USB Control Registers.........................................................................................................................................176

3.22.2.1 USB Function Address Register (USBFA) ........................................................................................................................176

3.22.2.2 USB Power Management Register (USBPM)....................................................................................................................176

3.22.2.3 USB Endpoint Interrupt Register (USBEPI)......................................................................................................................177

3.22.2.4 USB Interrupt Register (USBINT).....................................................................................................................................178

3.22.2.5 Endpoint Interrupt Enable Register (USBEPIEN)..............................................................................................................178

3.22.2.6 USB Interrupt Enable Register (USBINTEN)....................................................................................................................178

3.22.2.7 USB Low Byte Frame Number Register (USBLBFN).......................................................................................................178

3.22.2.8 USB High Byte Frame Number Register (USBHBFN) .....................................................................................................178

3.22.2.9 USB Index Register (USBIND) .........................................................................................................................................178

3.22.2.10

3.22.2.11

3.22.2.12

3.22.2.13

3.22.2.14

3.22.2.15

3.22.2.16

3.22.2.17

3.22.2.18

3.22.2.19

3.22.2.20

3.22.2.21

3.22.2.22

USB MAXP Register (USBMP)....................................................................................................................................179

USB EP0 Control Register (USBEP0CON) ..................................................................................................................179

USB IN Control 1 Register (USBICON1) .....................................................................................................................180

USB IN Control 2 Register (USBICON2) .....................................................................................................................180

USB OUT Control Register 1 (USBOCON1)................................................................................................................181

USB OUT Control Register 2 (USBOCON2)................................................................................................................181

USB Low Byte Out Write Count Register (USBLBOWC)............................................................................................181

USB High Byte Out Write Count Register (USBHBOWC) ..........................................................................................182

EP0 FIFO Data Register (USBEP0D)............................................................................................................................182

EP1 FIFO Data Register (USBEP1D)............................................................................................................................182

EP2 FIFO Data Register (USBEP2D)............................................................................................................................182

EP3 FIFO Data Register (USBEP3D)............................................................................................................................182

EP4 FIFO Data Register (USBEP4D)............................................................................................................................182

3.23 WATCH DOG TIMER .....................................................................................................................................................183

3.23.1 Watch Dog Timer Control Register (WDCON)...................................................................................................183

3.23.2 Watch Dog Timer Count Register (WDCNT) ......................................................................................................183

3.24 TIMER / PWM / CAPTURE.............................................................................................................................................184

3.24.1 Introduction .........................................................................................................................................................184

3.24.2 10bit Pre-scale.....................................................................................................................................................184

3.24.3 Timer/Counter .....................................................................................................................................................184

7

CONFIDENTIAL

Beijing Peak Microtech Co.Ltd.

ETC [ ETC ]

ETC [ ETC ]