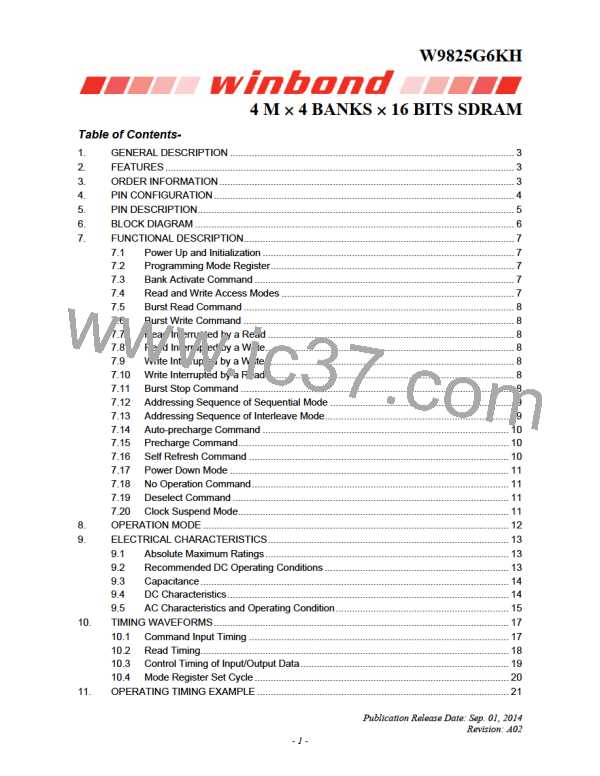

W9825G6KH

7.12 Addressing Sequence of Sequential Mode

A column access is performed by increasing the address from the column address which is input to

the device. The disturb address is varied by the Burst Length as shown in Table 2.

Table 2 Address Sequence of Sequential Mode

DATA

Data 0

Data 1

Data 2

Data 3

Data 4

Data 5

Data 6

Data 7

ACCESS ADDRESS

BURST LENGTH

n

BL = 2 (disturb address is A0)

No address carry from A0 to A1

BL = 4 (disturb addresses are A0 and A1)

No address carry from A1 to A2

n + 1

n + 2

n + 3

n + 4

n + 5

n + 6

n + 7

BL = 8 (disturb addresses are A0, A1 and A2)

No address carry from A2 to A3

7.13 Addressing Sequence of Interleave Mode

A column access is started in the input column address and is performed by inverting the address bit

in the sequence shown in Table 3.

Table 3 Address Sequence of Interleave Mode

DATA

ACCESS ADDRESS

BURST LENGTH

Data 0

A8 A7 A6 A5 A4 A3 A2 A1 A0

BL = 2

Data 1

Data 2

Data 3

Data 4

Data 5

Data 6

Data 7

A8 A7 A6 A5 A4 A3 A2 A1 A0

A8 A7 A6 A5 A4 A3 A2 A1 A0

A8 A7 A6 A5 A4 A3 A2 A1 A0

A8 A7 A6 A5 A4 A3 A2 A1 A0

A8 A7 A6 A5 A4 A3 A2 A1 A0

A8 A7 A6 A5 A4 A3 A2 A1 A0

A8 A7 A6 A5 A4 A3 A2 A1 A0

BL = 4

BL = 8

Publication Release Date: Sep. 01, 2014

Revision: A02

- 9 -

WINBOND [ WINBOND ]

WINBOND [ WINBOND ]