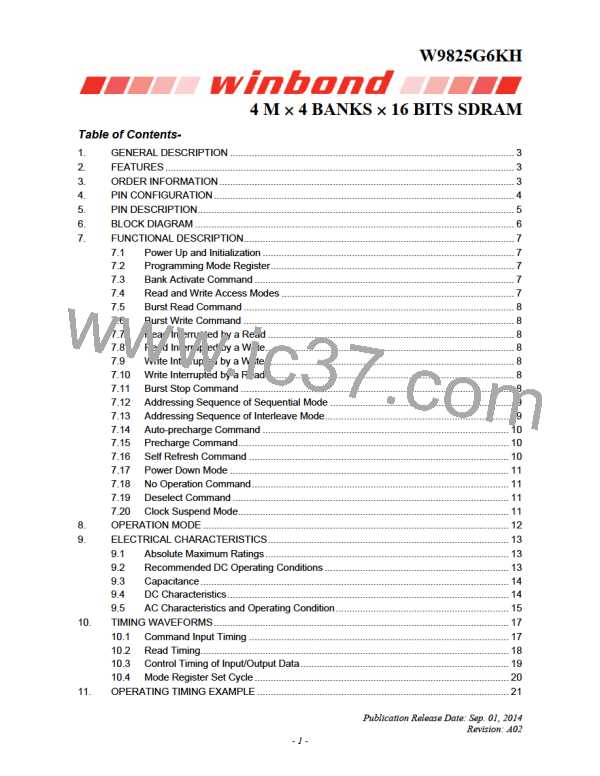

W9825G6KH

5. PIN DESCRIPTION

PIN NUMBER PIN NAME

FUNCTION

DESCRIPTION

A0A8Multiplexed pins for row and column address.

Row address: A0A12. Column address: A0A8.

2326, 22,

A0A12

2936

Address

Select bank to activate during row address latch time, or

bank to read/write during address latch time.

20, 21

BS0, BS1

Bank Select

2, 4, 5, 7, 8, 10,

11, 13, 42, 44,

45, 47, 48, 50,

51, 53

Data

Input/Output

Multiplexed pins for data output and input.

DQ0DQ15

Disable or enable the command decoder. When

19

18

Chip Select command decoder is disabled, new command is

ignored and previous operation continues.

CS

Command input. When sampled at the rising edge of

Row Address

RAS

the clock, RAS ,

CAS and WE define the

operation to be executed.

Strobe

Column

Address

Strobe

17

16

CAS

WE

Referred to RAS

Write Enable

Referred to RAS

The output buffer is placed at Hi-Z(with latency of 2)

LDQM,

UDQM

Input/Output when DQM is sampled high in read cycle. In write

15, 39

Mask

cycle, sampling DQM high will block the write

operation with zero latency.

System clock used to sample inputs on the rising edge

of clock.

38

37

CLK

CKE

Clock Inputs

CKE controls the clock activation and deactivation.

Clock Enable When CKE is low, Power Down mode, Suspend mode,

or Self Refresh mode is entered.

1, 14, 27

VDD

VSS

Power

Ground

Power

Power for input buffers and logic circuit inside DRAM.

Ground for input buffers and logic circuit inside DRAM.

Separated power from VDD, to improve DQ noise

28, 41, 54

3, 9, 43, 49

VDDQ

for I/O Buffer immunity.

Ground

for I/O Buffer immunity.

Separated ground from VSS, to improve DQ noise

6, 12, 46, 52

40

VSSQ

NC

No Connection No connection.

Publication Release Date: Sep. 01, 2014

Revision: A02

- 5 -

WINBOND [ WINBOND ]

WINBOND [ WINBOND ]