WED3DL644V

White Electronic Designs

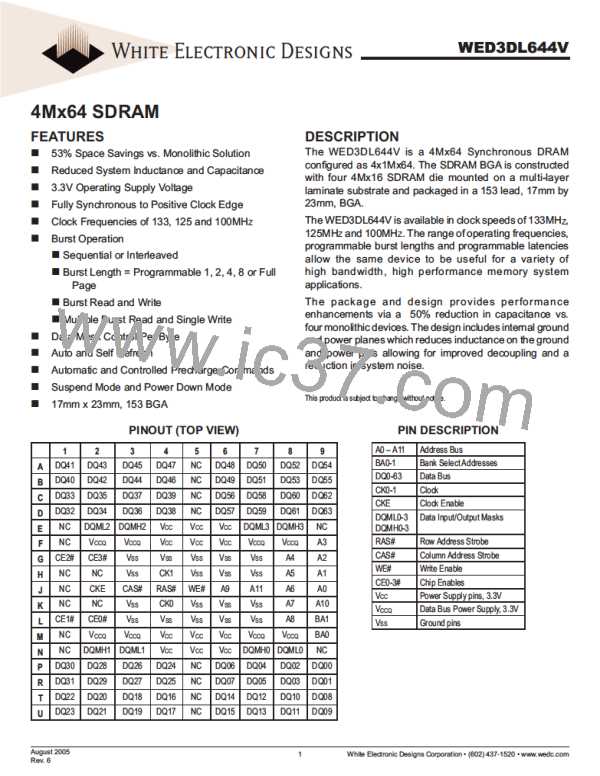

FIG. 13 WRITE INTERRUPTED BY PRECHARGE COMMAND & WRITE BURST STOP CYCLE

@BURST LENGTH=FULL PAGE

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

CLOCK

HIGH

CKE

CE#

RAS#

CAS#

ADDR

RAa

CAa

CAb

BA

A10/AP

DQ

RAa

tBDL

tRDL

Note 2

DAa0 DAa1 DAa2 DAa3 DAa4

DAb0 DAb1 DAb2 DAb3 DAb4 DAb5

WE#

DQM

Row Active

(A-Bank)

Write

(A-Bank)

Burst Stop

Write

(A-Bank)

Precharge

(A-Bank)

DON'T CARE

NOTES:

1.

2.

At full page mode, burst is end at the end of burst. So auto precharge is possible.

Data-in at the cycle of interrupted by precharge cannot be written into the corresponding memory cell. It is defined by AC parameter of tRDL

.

DQM at write interrupted by precharge command is needed to prevent invalid write.

DQM should mask invalid input data on precharge command cycle when asserting precharge before end of burst. Input data after Row precharge cycle

will be masked internally.

3.

Burst stop is valid at every burst length.

August 2005

Rev. 6

22

White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

WEDC [ WHITE ELECTRONIC DESIGNS CORPORATION ]

WEDC [ WHITE ELECTRONIC DESIGNS CORPORATION ]