WED3DL644V

White Electronic Designs

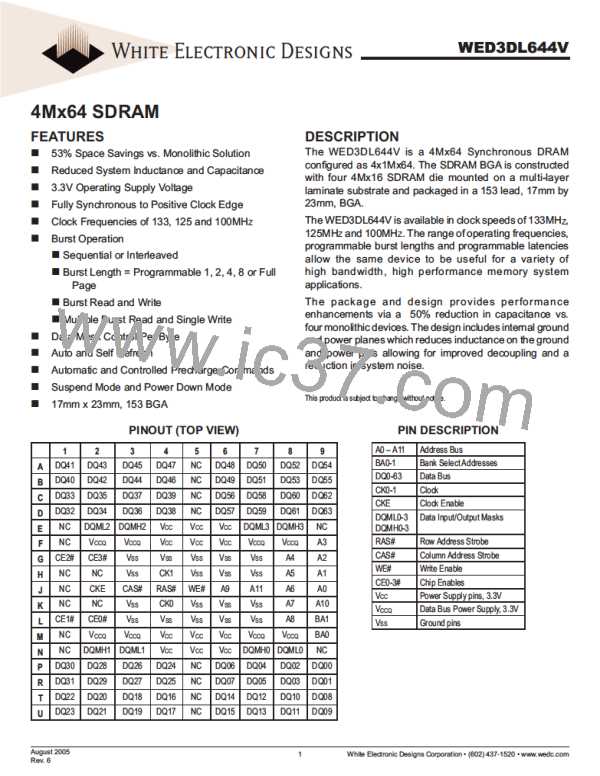

FIG. 11 CLOCK SUSPENSION & DQM OPERATION CYCLE @CAS LATENCY=2, BURST

LENGTH=4

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

CLOCK

CKE

CE#

RAS#

CAS#

ADDR

Ra

Ca

Cb

Cc

BA

Ra

A10/AP

tSHZ

tSHZ

DQ

Qa0

Qa1

Qa2

Qa3

Qb1

Qb1

Dc0

Dc2

WE#

Note 1

DQM

Row Active

Read

Clock

Suspension

Read

Write

DQM

Write

DQM

Read DQM

Clock

Suspension

Write

DON'T CARE

NOTE:

1.

DQM is needed to prevent bus contention.

August 2005

Rev. 6

20

White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

WEDC [ WHITE ELECTRONIC DESIGNS CORPORATION ]

WEDC [ WHITE ELECTRONIC DESIGNS CORPORATION ]