WED3DL644V

White Electronic Designs

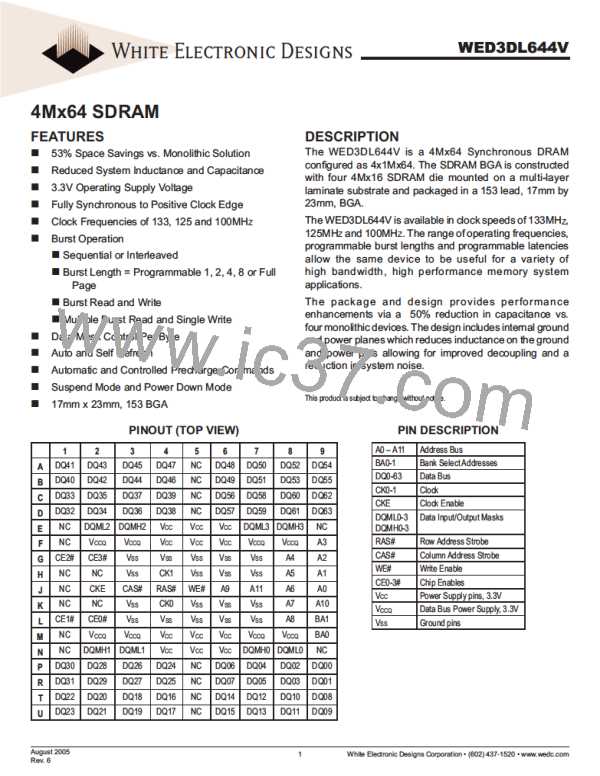

FIG. 16 SELF REFRESH ENTRY & EXIT CYCLE

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

CLOCK

Note 2

tRFC min

tSS

Note 4

Note 3

Note 6

Note 1

CKE

Note 5

CE#

RAS#

Note 7

CAS#

ADDR

BA

A

10/AP

DQ

HI-Z

HI-Z

WE#

DQM

Self Refresh Entry

Self Refresh Exit

Auto Refresh

DON'T CARE

NOTES:

TO ENTER SELF REFRESH MODE

1.

2.

3.

CE#, RAS# & CAS# with CKE should be low at the same clock cycle.

After 1 clock cycle, all the inputs including the system clock can be don't care except for CKE.

The device remains in self refresh mode as long as CKE stays "Low."

Once the device enters self refresh mode, minimum tras is required before exit from self refresh.

TO EXIT SELF REFRESH MODE

4.

5.

6.

7.

System clock restart and be stable before returning CKE high.

CE# starts from high.

Minimum tRFC is required after CKE going high to complete self refresh exit.

4K cycle of burst auto refresh is required before self refresh entry and after self refresh exit if the system uses burst refresh.

August 2005

Rev. 6

25

White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

WEDC [ WHITE ELECTRONIC DESIGNS CORPORATION ]

WEDC [ WHITE ELECTRONIC DESIGNS CORPORATION ]