WED3DL644V

White Electronic Designs

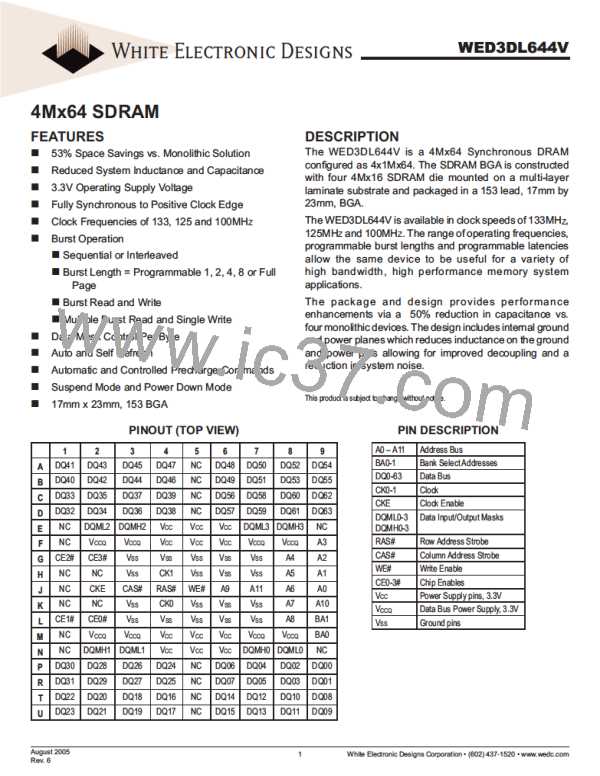

FIG. 7 PAGE READ CYCLE AT DIFFERENT BANK @BURST LENGTH=4

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

CLOCK

HIGH

CKE

Note 1

CE#

RAS#

Note 2

CAS#

ADDR

RAa

CAa

RBb

CBb

CAc

CBd

CAe

BA

A10/AP

CL = 2

RAa

RBb

QAa0 QAa1 QAa2 QAa3 QBb0 QBb1 QBb2 QBb3 QAc0 QAc1 QBd0 QBd1 QAe0 QAe1

DQ

CL = 3

QAa0 QAa1 QAa2 QAa3 QBb0 QBb1 QBb2 QBb3 QAc0 QAc1 QBd0 QBd1 QAe0 QAe1

WE#

DQM

Row Active

(A-Bank)

Row Active

(B-Bank)

Read

(B-Bank)

Read

(A-Bank)

Read

(B-Bank)

Read

(A-Bank)

Precharge

(A-Bank)

Read

(A-Bank)

DON'T CARE

NOTES:

1.

2.

CE# can be don't care when RAS#, CAS# and WE# are high at the clock high going edge.

To interrupt a burst read by row precharge, both the read and the precharge banks must be the same.

August 2005

Rev. 6

16

White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

WEDC [ WHITE ELECTRONIC DESIGNS CORPORATION ]

WEDC [ WHITE ELECTRONIC DESIGNS CORPORATION ]