TPS929160-Q1

ZHCSNG0 – APRIL 2023

www.ti.com.cn

Return to the Summary Table.

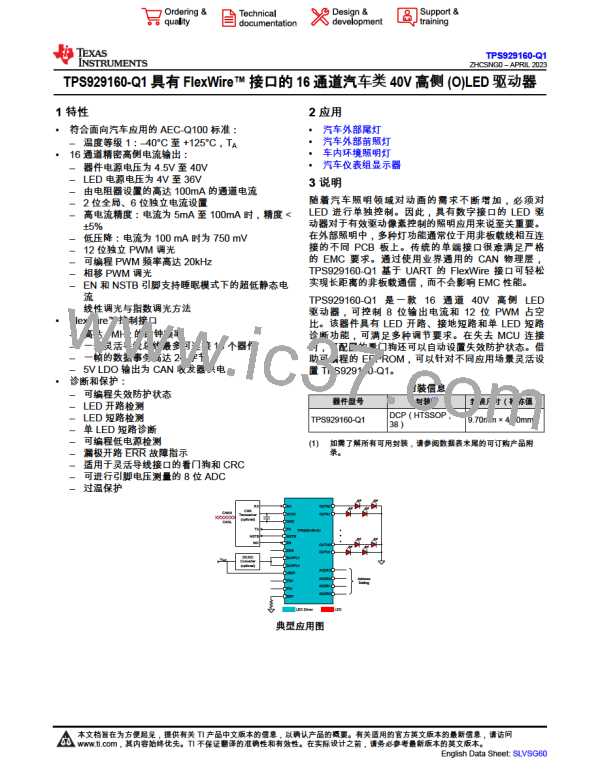

图 7-43. PWMMR6 Register

7

6

5

4

3

2

1

1

1

0

0

0

RESERVED

R-0h

表 7-43. PWMMR6 Register Field Descriptions

Bit

7-0

Field

RESERVED

Type

Reset

Description

R

0h

Reserved

7.6.1.24 PWMMR7 Register (Offset = 17h) [Reset = 00h]

PWMMR7 is shown in 图 7-44 and described in 表 7-44.

Return to the Summary Table.

图 7-44. PWMMR7 Register

7

6

5

4

3

2

RESERVED

R-0h

表 7-44. PWMMR7 Register Field Descriptions

Bit

7-0

Field

RESERVED

Type

Reset

Description

R

0h

Reserved

7.6.1.25 PWMLA0 Register (Offset = 20h) [Reset = 00h]

PWMLA0 is shown in 图 7-45 and described in 表 7-45.

Return to the Summary Table.

图 7-45. PWMLA0 Register

7

6

5

4

3

2

RESERVED

R-0h

PWMLOWOUTA0

R/W-0h

表 7-45. PWMLA0 Register Field Descriptions

Bit

Field

Type

Reset

Description

7-4

3-0

RESERVED

R

0h

Reserved

PWMLOWOUTA0

R/W

0h

4-LSB output PWM duty-cycle setting for OUTA0

7.6.1.26 PWMLA1 Register (Offset = 21h) [Reset = 00h]

PWMLA1 is shown in 图 7-46 and described in 表 7-46.

Return to the Summary Table.

图 7-46. PWMLA1 Register

7

6

5

4

3

2

1

0

RESERVED

R-0h

PWMLOWOUTA1

R/W-0h

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

67

Product Folder Links: TPS929160-Q1

English Data Sheet: SLVSG60

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]