TPS929160-Q1

ZHCSNG0 – APRIL 2023

www.ti.com.cn

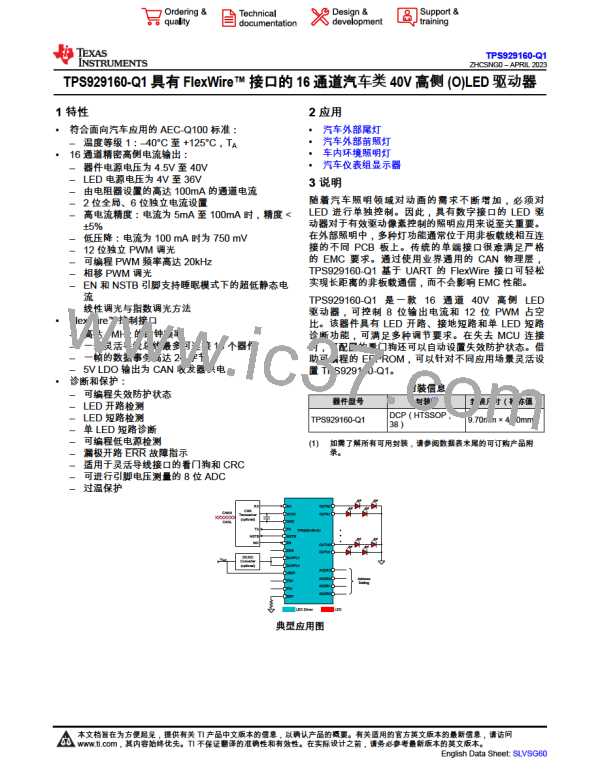

图 7-119. FLEXWIRE1 Register

7

6

5

4

3

2

1

0

RESERVED

R-0h

INTADDR

R/W-X

DEVADDR

R/W-X

表 7-123. FLEXWIRE1 Register Field Descriptions

Bit

7-5

4

Field

Type

Reset

Description

RESERVED

INTADDR

R

0h

Reserved

R/W

X

Devce address selection register

Load EEPROM data when reset

0h = Device address set by ADDR2/ADDR1 and ADDR0 pins

1h = Device address set by DEVADDR

3-0

DEVADDR

R/W

X

Device address setting register

Load EEPROM data when reset

0h = slave address is 0000b

1h = slave address is 0001b

2h = slave address is 0010b

3h = slave address is 0011b

4h = slave address is 0100b

5h = slave address is 0101b

6h = slave address is 0110b

7h = slave address is 0111b

8h = slave address is 1000b

9h = slave address is 1001b

Ah = slave address is 1010b

Bh = slave address is 1011b

Ch = slave address is 1100b

Dh = slave address is 1101b

Eh = slave address is 1110b

Fh = slave address is 1111b

7.6.3.23 FLEXWIRE2 Register (Offset = 86h) [Reset = X]

FLEXWIRE2 is shown in 图 7-120 and described in 表 7-124.

Return to the Summary Table.

图 7-120. FLEXWIRE2 Register

7

6

5

4

3

2

1

0

RESERVED

R-0h

OFAF

R/W-X

INITTIMER

R/W-X

表 7-124. FLEXWIRE2 Register Field Descriptions

Bit

Field

Type

Reset

Description

7-5

4

RESERVED

OFAF

R

0h

Reserved

R/W

X

Output one-fail-all-fail setting register in fail-safe state

Load EEPROM data when reset

0h = OFAF Disabled

1h = OFAF Enabled

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: SLVSG60

100 Submit Document Feedback

Product Folder Links: TPS929160-Q1

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]