TPS929160-Q1

ZHCSNG0 – APRIL 2023

www.ti.com.cn

表 7-118. FSMAP0 Register Field Descriptions (continued)

Bit

Field

Type

Reset

Description

5

FSOUTB1

R/W

X

Fail-safe state control input mapping for OUTB1

Load EEPROM data when reset

0h = OUTB1 is mapped to FS0 in fail-safe state

1h = OUTB1 is mapped to FS1 in fail-safe state

4

FSOUTB0

R/W

X

Fail-safe state control input mapping for OUTB0

Load EEPROM data when reset

0h = OUTB0 is mapped to FS0 in fail-safe state

1h = OUTB0 is mapped to FS1 in fail-safe state

3-2

1

RESERVED

FSOUTA1

R

0h

X

Reserved

R/W

Fail-safe state control input mapping for OUTA1

Load EEPROM data when reset

0h = OUTA1 is mapped to FS0 in fail-safe state

1h = OUTA1 is mapped to FS1 in fail-safe state

0

FSOUTA0

R/W

X

Fail-safe state control input mapping for OUTA0

Load EEPROM data when reset

0h = OUTA0 is mapped to FS0 in fail-safe state

1h = OUTA0 is mapped to FS1 in fail-safe state

7.6.3.18 FSMAP1 Register (Offset = 81h) [Reset = X]

FSMAP1 is shown in 图 7-115 and described in 表 7-119.

Return to the Summary Table.

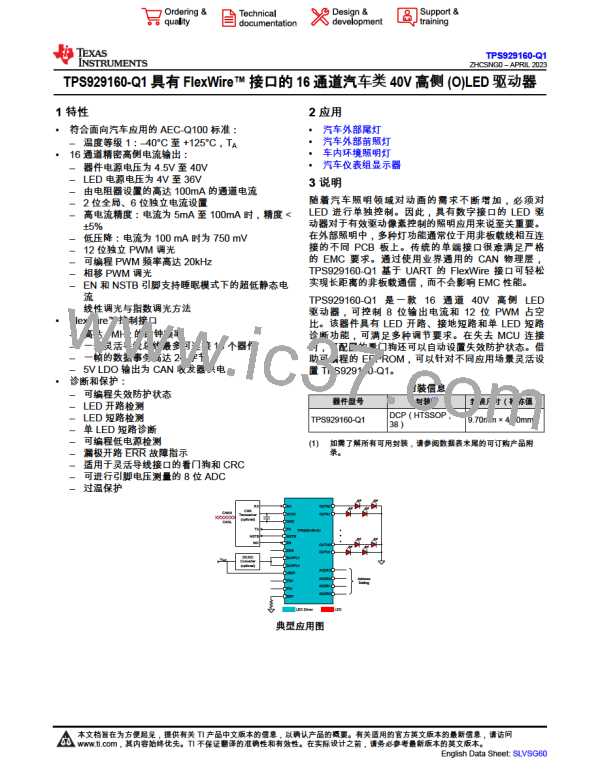

图 7-115. FSMAP1 Register

7

6

5

4

3

2

1

0

RESERVED

R-0h

FSOUTD1

R/W-X

FSOUTD0

R/W-X

RESERVED

R-0h

FSOUTC1

R/W-X

FSOUTC0

R/W-X

表 7-119. FSMAP1 Register Field Descriptions

Bit

Field

Type

Reset

Description

7-6

5

RESERVED

FSOUTD1

R

0h

Reserved

R/W

X

Fail-safe state control input mapping for OUTD1

Load EEPROM data when reset

0h = OUTD1 is mapped to FS0 in fail-safe state

1h = OUTD1 is mapped to FS1 in fail-safe state

4

FSOUTD0

R/W

X

Fail-safe state control input mapping for OUTC2

Load EEPROM data when reset

0h = OUTD0 is mapped to FS0 in fail-safe state

1h = OUTD0 is mapped to FS1 in fail-safe state

3-2

1

RESERVED

FSOUTC1

R

0h

X

Reserved

R/W

Fail-safe state control input mapping for OUTC1

Load EEPROM data when reset

0h = OUTC1 is mapped to FS0 in fail-safe state

1h = OUTC1 is mapped to FS1 in fail-safe state

0

FSOUTC0

R/W

X

Fail-safe state control input mapping for OUTC0

Load EEPROM data when reset

0h = OUTC0 is mapped to FS0 in fail-safe state

1h = OUTC0 is mapped to FS1 in fail-safe state

7.6.3.19 FSMAP2 Register (Offset = 82h) [Reset = X]

FSMAP2 is shown in 图 7-116 and described in 表 7-120.

Return to the Summary Table.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

97

Product Folder Links: TPS929160-Q1

English Data Sheet: SLVSG60

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]