ADVANCE

4 MEG x 8, 4 MEG x 9, 2 MEG x 18, 1 MEG x 36

1.8V VDD, HSTL, QDRIIb2 SRAM

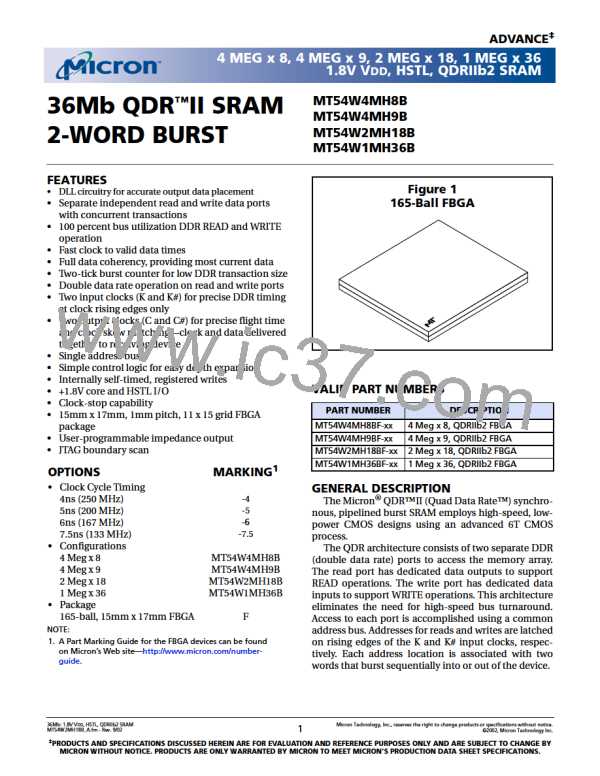

AC ELECTRICAL CHARACTERISTICS AND RECOMMENDED OPERATING

CONDITIONS 1, 2, 3, 6, 8

0ºC

?

TA

?

+70ºC; +1.7V ?ꢁVDD ? +1.9V

-4

-5

-6

-7.5

DESCRIPTION

SYMBOL

UNITS

MIN

MAX

5.00

0.20

MIN

MAX

6.00

0.20

MIN

MAX

7.50

0.20

MIN

MAX

8.00

0.20

Clock

tKHKH

tKC var

4.00

5.00

6.0

7.50

ns

ns

Clock cycle time

(K, K#, C, C#)4

Clock phase jitter

(K, K#, C, C#)5

tKHKL

tKLKH

Clock HIGH time

(K, K#, C, C#)

Clock LOW time

(K, K#, C, C#)

Clock to clock#

(KIJK#I, CIJC#I) at

tKHKH minimum

1.60

1.60

1.80

2.00

2.00

2.20

2.40

2.40

2.70

3.00

3.00

3.38

ns

ns

ns

tKHK#H

tK#HKH

tKHCH

1.80

0.00

2.20

0.00

2.70

0.00

3.38

0.00

ns

ns

Clock to clock#

(K#IJKI, C#IJCI)

Clock to data clock

(KIJCI, K#IJC#I)

1.80

2.30

2.80

3.55

tKC lock

tKC reset

DLL lock time (K, C)6

K static to DLL reset

1,024

30

1,024

30

1,024

30

1,024

30

cycles

ns

Output Times

C, C# HIGH to output valid

tCHQV

tCHQX

tCHCQV

0.40

0.33

0.43

0.36

0.45

0.38

0.45

0.38

ns

ns

ns

-0.40

-0.33

-0.43

-0.36

-0.45

-0.38

-0.45

-0.38

C, C# HIGH to output hold

C, C# HIGH to echo clock

valid

tCHCQX

tCQHQV

C, C# HIGH to echo clock

hold

CQ, CQ# HIGH to output

valid7

ns

ns

0.35

0.0

0.38

0.43

0.40

0.45

0.40

0.45

tCQHQX

-0.35

-0.38

-0.40

-0.40

ns

CQ, CQ# HIGH to output

hold7

tCHQZ

tCHQX1

ns

ns

C HIGH to output High-Z

C HIGH to output Low-Z

-0.40

0.40

0.40

0.40

-0.43

0.50

0.50

0.50

-0.45

0.60

0.60

0.60

-0.45

0.70

0.70

0.70

Setup Times

Address valid to K rising

edge8

Control inputs valid to K

rising edge8

tAVKH

tIVKH

ns

ns

ns

tDVKH

Data-in valid to K, K# rising

edge8

36Mb: 1.8V VDD, HSTL, QDRIIb2 SRAM

MT54W2MH18B_A.fm - Rev 9/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology Inc.

15

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]