ADVANCE

4 MEG x 8, 4 MEG x 9, 2 MEG x 18, 1 MEG x 36

1.8V VDD, HSTL, QDRIIb2 SRAM

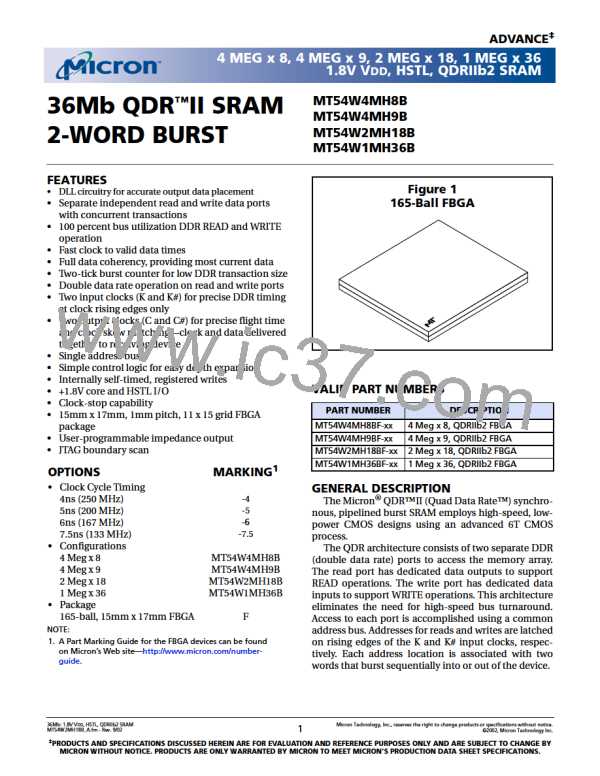

Figure 6

READ/WRITE Timing3

READ

WRITE

READ

WRITE

READ

WRITE

NOP

WRITE

NOP

(Note 2)

6

1

2

3

4

5

7

8

10

9

K

t

t

t

t

KHKL

KLKH

KHKH

KHK#H

K#

R#

t

t

KHIX

IVKH

W#

A

(Note 3)

t

A5

A6

A0

A1

t

A2

A3

A4

t

t

AVKH KHAX AVKH KHAX

D

Q

D10

D11

D30

D31

D50

D51

Q01

D60

Q20

D61

t

t

KHDX

t

t

KHDX

DVKH

DVKH

(Note 1)

Q00

Q21

Q40

Q41

t

CHQZ

t

CHQX1

t

t

CHQX

t

CQHQV

CHQX

t

KHCH

t

KLKH

t

t

CHQV

CHQV

C

C#

t

KHKL

t

t

KHKH

KHK#H

t

KHCH

t

CHCQV

CHCQX

t

CQ

t

CHCQV

CHCQX

t

CQ#

DON’T CARE

UNDEFINED

NOTE:

1. Q00 refers to output from address A0. Q01 refers to output from the next internal burst address following

A0, i.e., A0 + 1.

2. Outputs are disabled (High-Z) one clock cycle after a NOP.

3. In this example, if address A0 =ꢁA1, then data Q00 = D10, Q01 = D11. Write data is forwarded immediately as read results.

36Mb: 1.8V VDD, HSTL, QDRIIb2 SRAM

MT54W2MH18B_A.fm - Rev 9/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology Inc.

18

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]