ADVANCE

4 MEG x 8, 4 MEG x 9, 2 MEG x 18, 1 MEG x 36

1.8V VDD, HSTL, QDRIIb2 SRAM

AC TEST CONDITIONS

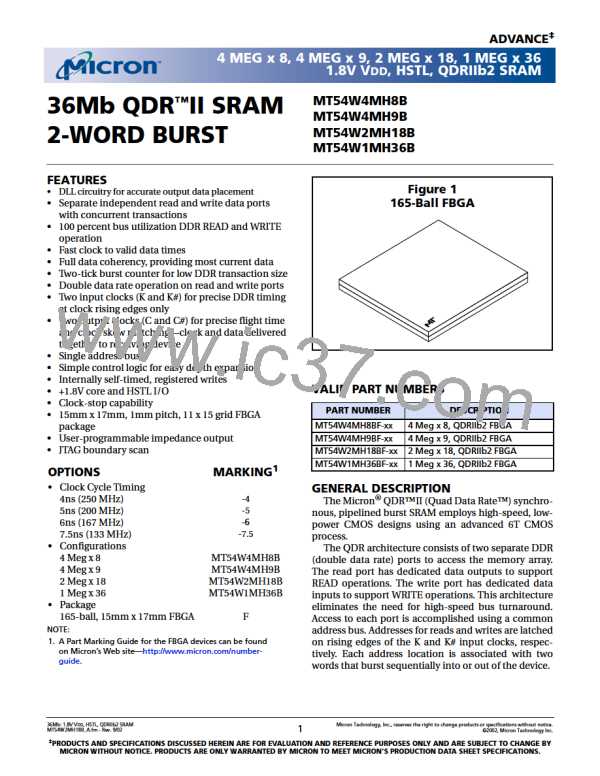

Figure 5

Output Load Equivalent

Input pulse levels . . . . . . . . . . . . . . . . . . 0.25V to 1.25V

Input rise and fall times . . . . . . . . . . . . . . . . . . . . 0.7ns

Input timing reference levels . . . . . . . . . . . . . . . . 0.75V

Output reference levels . . . . . . . . . . . . . . . . . . .VDDQ/2

ZQ for 50ꢀ impedance . . . . . . . . . . . . . . . . . . . . . 250ꢀ

Output load . . . . . . . . . . . . . . . . . . . . . . . . . See Figure 5

0.75V

VDDQ/2

VREF

50Ω

Z

= 50Ω

O

SRAM

250Ω

ZQ

36Mb: 1.8V VDD, HSTL, QDRIIb2 SRAM

MT54W2MH18B_A.fm - Rev 9/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology Inc.

17

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]