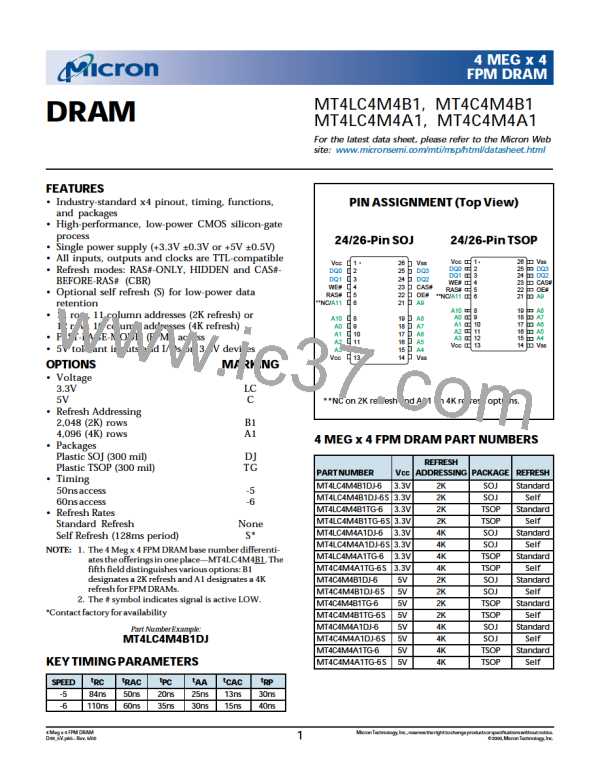

4 MEG x 4

FPM DRAM

AC ELECTRICAL CHARACTERISTICS

(Notes: 5, 6, 7, 8, 9, 10, 11, 12) [Vcc (MIN) £ Vcc £ Vcc (MAX)]

ACCHARACTERISTICS

-5

-6

PARAMETER

SYMBOL

MIN

MAX

MIN

MAX

UNITS

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

NOTES

t

Access time from column address

Column-addresshold time (referenced to RAS#)

Column-addresssetup time

Row-addresssetup time

AA

25

30

t

AR

38

0

45

0

t

ASC

t

ASR

0

0

t

Column address to WE# delay time

Access time from CAS#

AWD

42

49

18

t

CAC

13

15

t

Column-addresshold time

CAS# pulse width

CAH

8

8

10

10

15

10

0

t

CAS

10,000

10,000

t

CAS# LOW to “Don’t Care” during Self Refresh

CAS# hold time (CBR Refresh)

CAS# to output in Low-Z

CAS# precharge time

CHD

15

8

t

CHR

4

t

CLZ

0

22

13

t

CP

8

10

t

Access time from CAS# precharge

CAS# to RAS# precharge time

CAS# hold time

CPA

28

35

t

CRP

5

38

5

5

45

5

t

CSH

t

CAS# setup time (CBR Refresh)

CAS# to WE# delay time

WRITE command to CAS# lead time

Data-in hold time

CSR

4

t

CWD

28

8

35

10

10

0

18

t

CWL

t

DH

8

19

19

22

20

t

Data-in setup time

DS

0

t

Output disable

OD

0

12

12

0

15

15

t

Output enable

OE

t

OE# hold time from WE# during

READ-MODIFY-WRITEcycle

OEH

8

10

t

Output buffer turn-off delay

OFF

0

0

12

50

0

0

15

60

ns

ns

ns

ns

ns

ns

ns

ns

ns

µs

ns

ns

ns

ns

ms

ms

17, 22

t

OE# setup prior to RAS# during HIDDEN REFRESH cycle

FAST-PAGE-MODE READ or WRITE cycle time

FAST-PAGE-MODEREAD-WRITEcycle time

Access time from RAS#

ORD

t

PC

20

47

25

56

t

PRWC

t

RAC

t

RAS# to column-address delay time

Row-addresshold time

RAD

9

9

12

10

60

60

100

104

14

0

15

t

RAH

t

RAS# pulse width

RAS

50

50

100

84

11

0

10,000

10,000

t

RAS# pulse width (FASTPAGEMODE)

RAS# pulse width during Self Refresh

Random READ or WRITE cycle time

RAS# to CAS# delay time

RASP

125,000

125,000

t

RASS

t

RC

t

RCD

14

16

t

READcommand hold time (referenced to CAS#)

READcommand setup time

RCH

t

RCS

0

0

t

Refresh period (2,048 cycles)

REF

32

64

32

64

t

Refresh period (4,096 cycles)

REF

4 Meg x 4 FPM DRAM

D49_5V.p65 – Rev. 5/00

Micron Technology, Inc., reservesthe right to change productsor specificationswithout notice.

©2000, Micron Technology, Inc.

6

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]