4 MEG x 4

FPM DRAM

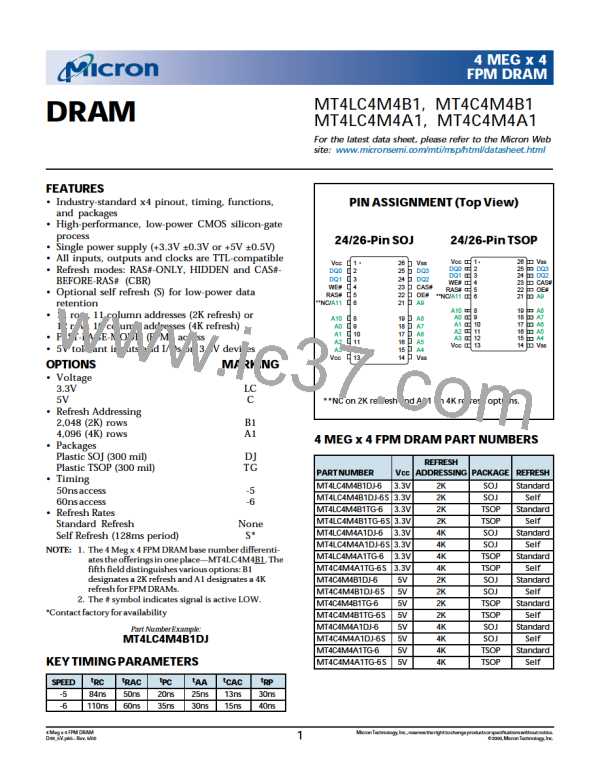

FUNCTIONAL BLOCK DIAGRAM – 2K REFRESH

WE#

CAS#

4

DATA-IN

BUFFER

DQ0

DQ1

DQ2

DQ3

4

DATA-OUT

BUFFER

NO. 2 CLOCK

GENERATOR

4

OE#

COLUMN-

ADDRESS

BUFFER(11)

COLUMN

DECODER

10

1

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

11

4

1,024

REFRESH

CONTROLLER

SENSE AMPLIFIERS

I/O GATING

1,024

REFRESH

COUNTER

2,048

2,048

2,048

11

4,096 x 1,024 x 4

MEMORY

ROW-

ADDRESS

BUFFERS (11)

ARRAY

11

11

2,048

2,048

NO. 1 CLOCK

GENERATOR

V

V

DD

SS

RAS#

FUNCTIONAL BLOCK DIAGRAM – 4K REFRESH

WE#

CAS#

4

4

DATA-IN

BUFFER

DQ0

DQ1

DQ2

DQ3

DATA-OUT

BUFFER

NO. 2 CLOCK

GENERATOR

4

OE#

COLUMN-

ADDRESS

BUFFER(10)

COLUMN

DECODER

10

A0

A1

10

4

1,024

A2

REFRESH

CONTROLLER

A3

SENSE AMPLIFIERS

I/O GATING

A4

A5

1,024

A6

REFRESH

COUNTER

A7

A8

12

A9

4,096 x 1,024 x 4

MEMORY

4,096

4,096

A10

A11

ROW-

ADDRESS

BUFFERS (12)

ARRAY

12

12

4,096

NO. 1 CLOCK

GENERATOR

V

DD

RAS#

Vss

4 Meg x 4 FPM DRAM

D49_5V.p65 – Rev. 5/00

Micron Technology, Inc., reservesthe right to change productsor specificationswithout notice.

©2000, Micron Technology, Inc.

3

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]