4 MEG x 4

FPM DRAM

READ CYCLE

t

RC

t

t

t

RAS

RP

V

V

IH

IL

RAS#

CAS#

t

CSH

t

RSH

RRH

t

t

t

RCD

CAS

CRP

V

V

IH

IL

t

AR

t

t

RAD

RAH

t

t

ASC

t

ASR

CAH

V

V

IH

IL

ROW

COLUMN

ROW

ADDR

WE#

t

t

RCS

RCH

V

V

IH

IL

t

t

t

t

AA

RAC

CAC

CLZ

t

OFF

V

V

IOH

IOL

DQ

OPEN

OPEN

VALID DATA

DON’T CARE

UNDEFINED

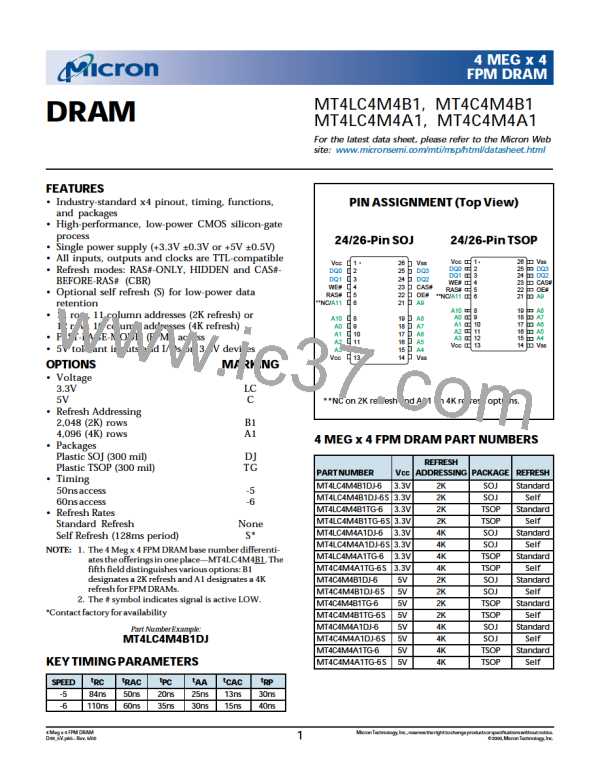

TIMING PARAMETERS

-5

-6

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

ns

SYMBOL

MIN

MAX

12

MIN

MAX

15

UNITS

ns

t

t

AA

25

30

OFF

0

0

t

t

AR

38

0

45

0

ns

RAC

50

60

ns

t

t

ASC

ns

RAD

9

9

12

10

60

104

14

0

ns

t

t

ASR

0

0

ns

RAH

ns

t

t

CAC

13

15

ns

RAS

50

84

11

0

10,000

10,000

ns

t

t

CAH

8

8

10

10

0

ns

RC

ns

t

t

CAS

10,000

10,000

ns

RCD

ns

t

t

CLZ

0

ns

RCH

ns

t

t

CRP

5

5

ns

RCS

0

0

ns

t

t

CSH

38

0

45

0

ns

RP

30

0

40

0

ns

t

t

OD

12

12

15

15

ns

RRH

ns

t

t

OE

ns

RSH

13

15

ns

4 Meg x 4 FPM DRAM

D49_5V.p65 – Rev. 5/00

Micron Technology, Inc., reservesthe right to change productsor specificationswithout notice.

©2000, Micron Technology, Inc.

9

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]