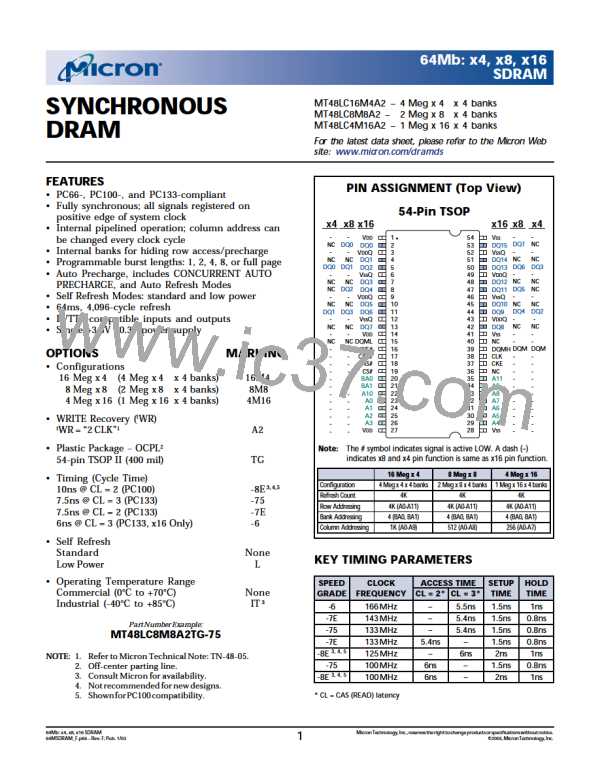

64Mb : x4, x8, x16

SDRAM

PRECHARGE com m and is that it requires that the com -

m and and address buses be available at the appropri-

ate tim e to issue the com m and; the advantage of the

PRECHARGE com m and is that it can be used to trun-

cate fixed-length or full-page bursts.

Full-page READ bursts can be truncated with the

BURST TERMINATE com m and, and fixed-length READ

bursts m ay be truncated with a BURST TERMINATE

com m and, provided that auto precharge was not acti-

vated. The BURST TERMINATE com m and should be

issued x cycles before the clock edge at which the last

desired data elem ent is valid, where x equals the CAS

latency m inus one. This is shown in Figure 12 for each

possible CAS latency; data elem ent n + 3 is the last

desired data elem ent of a longer burst.

Fig u re 12

Te rm in a t in g a READ Bu rst

T0

T1

T2

T3

T4

T5

T6

CLK

BURST

TERMINATE

READ

NOP

NOP

NOP

NOP

NOP

COMMAND

ADDRESS

DQ

X = 1 cycle

BANK,

COL n

D

OUT

D

n + 1

OUT

DOUT

DOUT

n + 3

n

n + 2

CAS Latency = 2

T0

T1

T2

T3

T4

T5

T6

T7

CLK

COMMAND

ADDRESS

DQ

BURST

TERMINATE

READ

NOP

NOP

NOP

NOP

NOP

NOP

X = 2 cycles

BANK,

COL n

D

OUT

DOUT

D

n + 2

OUT

DOUT

n + 3

n

n + 1

CAS Latency = 3

TRANSITIONING DATA

DON’T CARE

NOTE: DQM is LOW.

64Mb: x4, x8, x16 SDRAM

64MSDRAM_F.p65 – Rev. F; Pub. 1/03

Micron Technology, Inc., reservesthe right to change productsor specificationswithout notice.

©2003, Micron Technology, Inc.

20

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]