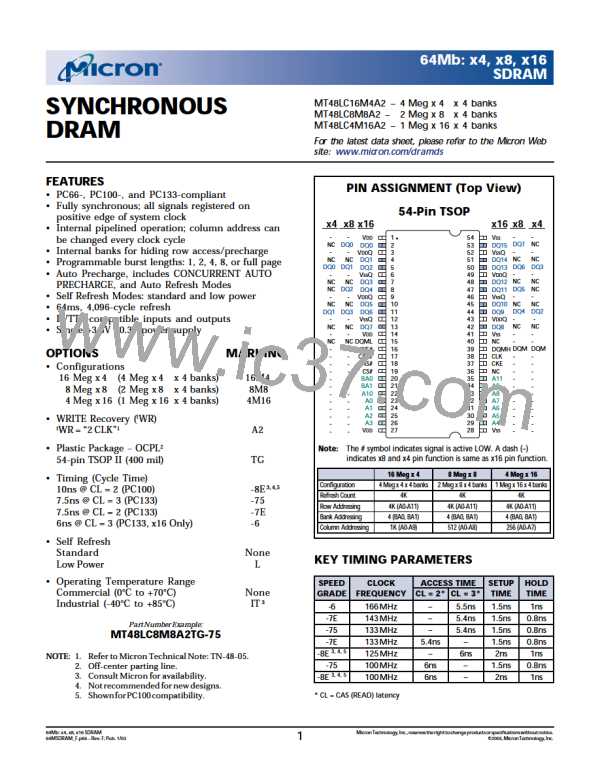

64Mb : x4, x8, x16

SDRAM

A fixed-length READ burst m ay be followed by, or

truncated with, a PRECHARGE com m and to the sam e

ban k (provided that auto precharge was n ot acti-

vated), and a full-page burst m ay be truncated with a

PRECHARGE com m an d to th e sam e b an k. Th e

PRECHARGE com m and should be issued x cycles be-

fore the clock edge at which the last desired data ele-

m ent is valid, where x equals the CAS latency m inus

one. This is shown in Figure 11 for each possible CAS

latency; data elem ent n + 3 is either the last of a burst of

four or the last desired of a longer burst. Following the

PRECHARGE com m and, a subsequent com m and to

the sam e bank cannot be issued until RP is m et. Note

that part of the row precharge tim e is hidden during

the access of the last data elem ent(s).

In the case of a fixed-length burst being executed to

com pletion, a PRECHARGE com m and issued at the

optim um tim e (as described above) provides the sam e

operation that would result from the sam e fixed-length

burst with auto precharge. The disadvantage of the

t

Fig u re 11

READ t o PRECHARGE

T0

T1

T2

T3

T4

T5

T6

T7

CLK

t

RP

READ

NOP

NOP

NOP

PRECHARGE

NOP

NOP

ACTIVE

COMMAND

ADDRESS

DQ

X = 1 cycle

BANK

(a or all)

BANK a,

COL n

BANK a,

ROW

D

OUT

D

n + 1

OUT

DOUT

DOUT

n + 3

n

n + 2

CAS Latency = 2

T0

T1

T2

T3

T4

T5

T6

T7

CLK

t

RP

READ

NOP

NOP

NOP

PRECHARGE

NOP

NOP

ACTIVE

COMMAND

ADDRESS

DQ

X = 2 cycles

BANK

(a or all)

BANK a,

COL n

BANK a,

ROW

D

OUT

DOUT

D

n + 2

OUT

DOUT

n + 3

n

n + 1

CAS Latency = 3

TRANSITIONING DATA

DON’T CARE

NOTE: DQM is LOW.

64Mb: x4, x8, x16 SDRAM

64MSDRAM_F.p65 – Rev. F; Pub. 1/03

Micron Technology, Inc., reservesthe right to change productsor specificationswithout notice.

©2003, Micron Technology, Inc.

19

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]