2 MEG x 16

ASYNC/PAGE/BURST FLASH MEMORY

1

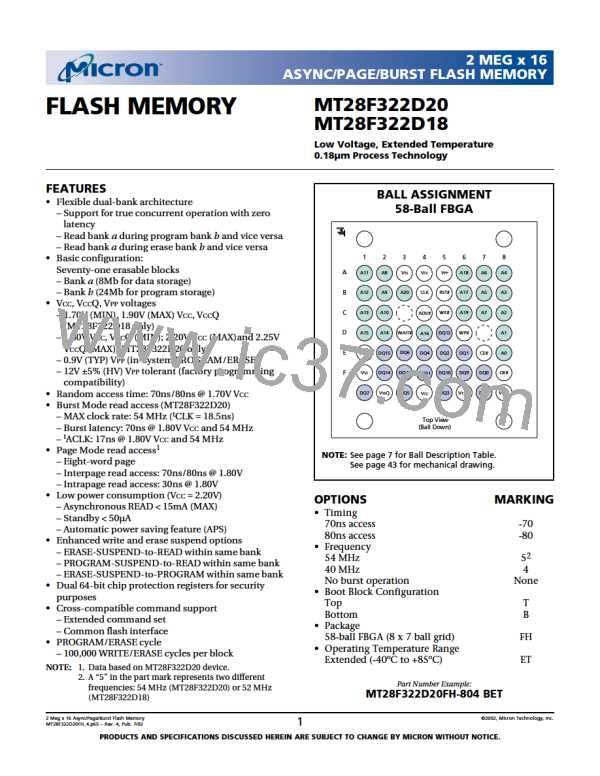

ASYNCHRONOUS READ CYCLE TIMING REQUIREMENTS

MT28F322D20 (VCC = 1.80V–2.25V) and MT28F322D18 (VCC = 1.70V–1.90V)

-70

-80

PARAMETER

SYMBOL

MIN

10

10

MAX

MIN

10

10

MAX

UNITS

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

t

Address setup to ADV# HIGH

CE# LOW to ADV# HIGH

READ cycle time

Address to output delay

CE# LOW to output delay

ADV# LOW to output delay

ADV# pulse width LOW

ADV# pulse width HIGH

Address hold from ADV# HIGH

Page address access

OE# LOW to output delay

RST# HIGH to output delay

CE# or OE# HIGH to output High-Z

Output hold from address, CE# or OE# change

AVS

t

CVS

RC

AA

t

70

70

70

70

80

80

80

80

t

t

ACE

t

AADV

t

VP

VPH

AVH

APA

10

10

3

10

10

3

t

t

t

30

25

200

15

30

30

200

25

t

AOE

t

RWH

t

OD

OH

t

0

0

NOTE: 1. See Figures 15 and 16 for timing requirements and load configuration.

2 Meg x 16 Async/Page/Burst Flash Memory

MT28F322D20FH_4.p65 – Rev. 4, Pub. 7/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology, Inc.

31

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]