†

LEGEND:

MANTISSA (1.0 - 1.9375)

0

R R

E E

G G

HI/LO

R

E

G

ACCUMULATOR

W/ PROGRAMMABLE

LIMITS

ACC = ACCUMULATOR

LMT = LIMIT

LEVEL

DETECT

7

EXPONENT (2 - 2 )

SIN/COS

VECTOR FROM

CARRIER NCO

CIC SCALER

R

= DOWN SAMPLER

LEVEL

DETECT

-36

CIC SHIFTER

LOOP

GAIN

2

MUX = MULTIPLEXER

REG = REGISTER

0

-63

+

2 -2

REG

REG

IIN0-9/

QIN0-9

† INDICATES ELEMENTS RUNNING

1ST ORDER CIC (I & D FILTER)

COMPENSATION

FILTER

R

E

G

R

E

G

R R R

E E E

G G G

A

C

C

AT THE OUTPUT SAMPLE RATE

R

X

31

SERIALIZE

-1

1

2

COMPLEX

MULTIPLIER

†

†

R

E

G

FROM

PROGRAMMABLE

DIVIDER

L

M

T

M

U

X

L

M

T

M

U

X

R R R R R

E E E E E

G G G G G

IOUT0-9/

QOUT0-9

11 TAP

FIR FILTER

+

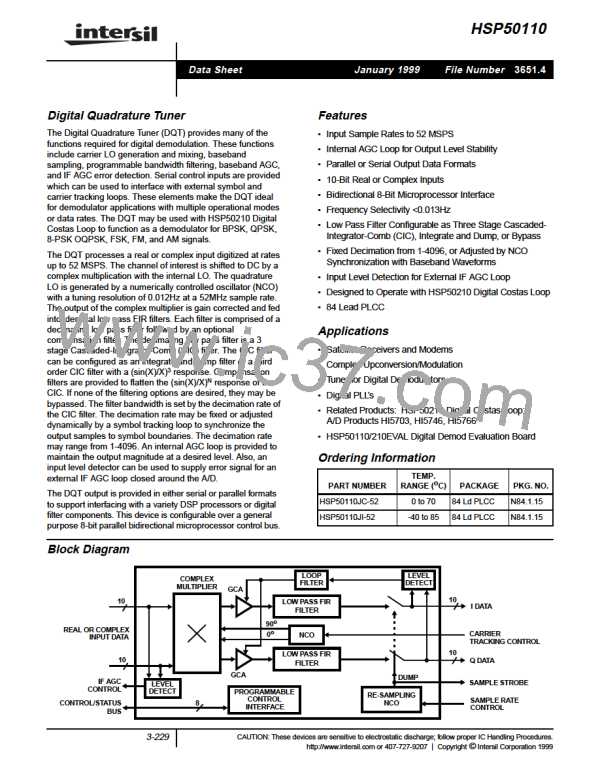

FIGURE 18. DATA FLOW FOR INTEGRATE/DUMP CONFIGURATION

†

LEGEND:

MANTISSA (1.0 - 1.9375)

R R

E E

G G

HI/LO

R

E

G

ACCUMULATOR

W/ PROGRAMMABLE

LIMITS

LEVEL

DETECT

ACC = ACCUMULATOR

LMT = LIMIT

0

7

EXPONENT (2 - 2 )

SIN/COS

VECTOR FROM

CARRIER NCO

CIC SCALER

1

CIC SHIFTER

R

= DOWN SAMPLER

LEVEL

DETECT

LOOP

GAIN

-36

0

-63

2

+

2 -2

MUX = MULTIPLEXER

REG = REGISTER

(TOP BITS ALIGNED)

REG

REG

3RD ORDER CIC FILTER

COMPENSATION

FILTER

IIN0-9/

QIN0-9

† INDICATES ELEMENTS RUNNING

R

E

G

R

E

G

R R R

E E E

G G G

A

C

C

A

C

C

A

C

C

AT THE OUTPUT SAMPLE RATE

R

X

55

-1

3

-3

1

SERIALIZE

IOUT0-9/

COMPLEX

MULTIPLIER

†

R

E

G

†

†

R

E

G

†

FROM

BIT RATE

NCO

QOUT0-9

R

E

G

L

M

T

M

U

X

L

M

T

M

U

X

R R R R R

E E E E E

G G G G G

15 TAP

FIR FILTER

+

+

+

FIGURE 19. DATA FLOW FOR 3RD ORDER CIC CONFIGURATION

LEGEND:

MANTISSA (1.0 - 1.9375)

0

ACC = ACCUMULATOR

LMT = LIMIT

R

E

G

ACCUMULATOR

W/ PROGRAMMABLE

LIMITS

LEVEL

DETECT

R R

E E

G G

HI/LO

7

EXPONENT (2 - 2 )

R

= DOWN SAMPLER

MUX = MULTIPLEXER

REG = REGISTER

SIN/COS

VECTOR FROM

CARRIER NCO

LOOP

GAIN

CIC SCALER

REG

REG

LEVEL

DETECT

-36

2

CIC SHIFTER

SERIALIZE

+

COMPENSATION

FILTER

0

-63

2 -2

IIN0-9/

QIN0-9

R

E

G

R

E

G

R R R

E E E

G G G

L

M

T

M

U

X

L

M

T

M

U

X

R R R R R

E E E E E

G G G G G

IOUT0-9/

QOUT0-9

11-15 TAP

X

FIR FILTER

21

COMPLEX

MULTIPLIER

FIGURE 20. DATA FLOW WITH CIC STAGE BYPASSED

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]