HI-3593

FUNCTIONAL DESCRIPTION (cont.)

RECEIVED ARINC 429 WORD

TO FILTERS (S/D, LABEL, PRIORITY-LABEL)

DATA

PARITY

CHECK

32 BIT SHIFT REGISTER

WORD

GAP

WORD GAP

TIMER

ONES

NULL

SHIFT REGISTER

SHIFT REGISTER

SHIFT REGISTER

EOS

END

BIT

CLOCK

NEW WORD

BIT

COUNTER

AND

END OF

1MHz

SEQUENCE

CONTROL

32ND

BIT

START

SEQUENCE

1MHz

1MHz

ZEROS

ERROR

ERROR

DETECTION

1MHz

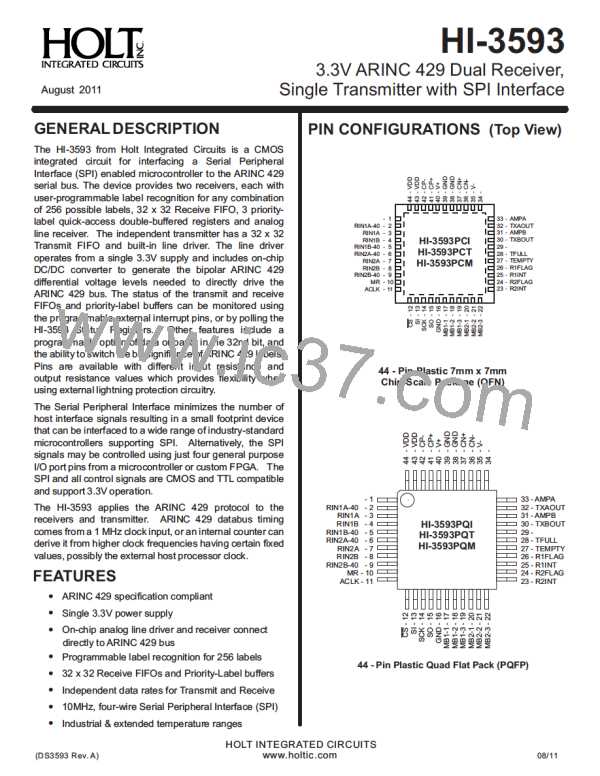

FIGURE 3. RECEIVER BLOCK DIAGRAM

RECEIVE DATA FIFO

RETRIEVING DATA

Each time a valid ARINC 429 word is loaded into the FIFO, the

Receive FIFO Status Register FFEMPTY, FFHALF and FFFULL bits

are updated. When the FIFO is EMPTY, the FFEMPTY bit is a “1” and

FFHALF and FFFULL are “0”. Once the first received and accepted

ARINC 429 word is loaded into the FIFO, FFEMPTY goes low. Each

receivedARINC 429 word is retrieved via the SPI interface using SPI

Op-Code 0xA0 (Receiver 1) or 0xC0 (Receiver 2).

Following S/D Filtering, accepted ARINC 429 words are

conditionally stored in the Receive FIFO. If label filtering is

disabled, all words are stored. If label filtering is enabled, the

incoming ARINC429 word’s label byte value is checked against its

corresponding bit in the pre-programmed label look-up table. If the

bit is set to a “1” the word is stored in the FIFO. If the bit is a “0” the

word is not stored in the FIFO.

Up to 32 ARINC 429 words may be held in the Receive FIFO.

FFFULL goes high when the Receive FIFO is full. Failure to unload

the Receive FIFO when full causes additional valid ARINC 429

words to overwrite Receive FIFO location 32.

LABEL RECOGNITION

The user loads the 256-bit label look-up table to specify which 8-bit

incoming ARINC labels are stored in the Receive FIFO, and which

are not. Setting a “1” in the look-up table enables processing of

received ARINC words containing the corresponding label. A “0”

in the look-up table causes discard of received ARINC words

containing the label. The 256-bit look-up table is loaded using SPI

Op-Codes 0x14 (Receiver 1) and 0x28 (Receiver 2), as described

in Table 1. After the look-up table is initialized, the Control Register

bit LABREC must be set to enable label recognition.

A FIFO half-full flag (FFHALF) is high whenever the Receive FIFO

contains 16 or more words. The FFHALF bit provides a useful

indicator to the host CPU that a sixteen word data retrieval routine

may be performed.

The FFEMPTY, FFHALF or FFFULLstatus bits can also be output on

the R1FLAG (Receiver 1) and R2FLAG (Receiver 2) pins. Flag /

Interrupt Assignment Register bits 5, 4, 1 and 0 select which flag

appears. Additionally, a FIFO not empty option may be programmed

for the R1FLAG / R2FLAG pins causing the pin to go high any time at

least one word is available in the FIFO.

All four bytes of the incoming ARINC429 word are stored in the

FIFO.

Table 3. defines the rules for Receive FIFO loading.

READING THE LABELLOOK-UPTABLE

The contents of the Label Look-up table may be read via the SPI

interface using Op-Code 0x98 (Receiver 1) or 0xB8 (Receiver 2) as

described inTable 1.

HOLT INTEGRATED CIRCUITS

11

HOLTIC [ HOLT INTEGRATED CIRCUITS ]

HOLTIC [ HOLT INTEGRATED CIRCUITS ]