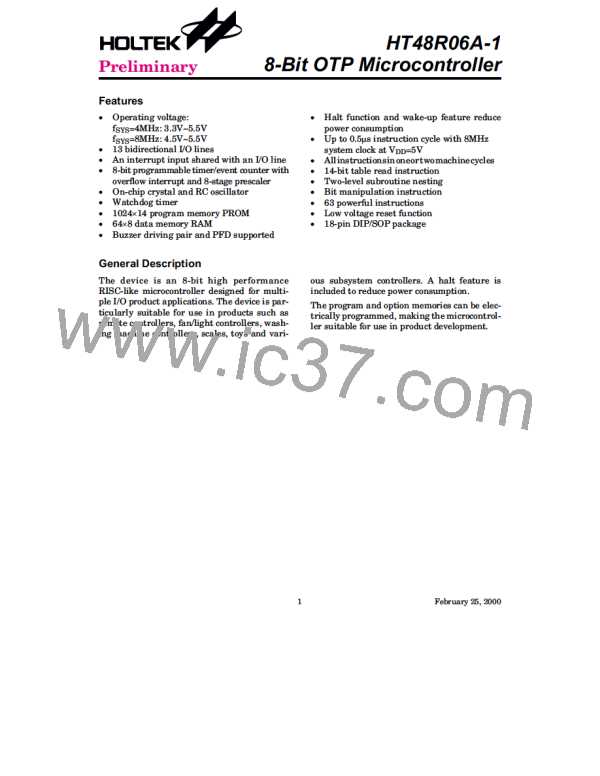

Preliminary

HT48R06A-1

tions related to the status register may give

different results from those intended. The

TO flag can be affected only by system

power-up, a WDT time-out or executing the

"CLR WDT" or "HALT" instruction. The PD

flag can be affected only by executing the

"HALT" or "CLR WDT" instruction or a sys-

tem power-up.

the other interrupts will be blocked (by clearing

the EMI bit). This scheme may prevent any fur-

ther interrupt nesting. Other interrupt re-

quests may happen during this interval but

only the interrupt request flag is recorded. If a

certain interrupt requires servicing within the

service routine, the EMI bit and the correspond-

ing bit of INTC may be set to allow interrupt

nesting. If the stack is full, the interrupt request

will not be acknowledged, even if the related in-

terrupt is enabled, until the SP is decremented.

If immediate service is desired, the stack must

be prevented from becoming full.

The Z, OV, AC and C flags generally reflect the

status of the latest operations.

In addition, on entering the interrupt sequence

or executing the subroutine call, the status reg-

ister will not be pushed onto the stack automat-

ically. If the contents of the status are

important and if the subroutine can corrupt the

status register, precautions must be taken to

save it properly.

All these kinds of interrupts have a wake-up ca-

pability. As an interrupt is serviced, a control

transfer occurs by pushing the program counter

onto the stack, followed by a branch to a sub-

routine at specified location in the program

memory. Only the program counter is pushed

onto the stack. If the contents of the register or

status register (STATUS) are altered by the in-

terrupt service program which corrupts the de-

sired control sequence, the contents should be

saved in advance.

Interrupt

The device provides an external interrupt and

internal timer/event counter interrupts. The

Interrupt Control Register (INTC;0BH) con-

tains the interrupt control bits to set the en-

able/disable and the interrupt request flags.

External interrupts are triggered by a high to

low transition of INT and the related interrupt

Once an interrupt subroutine is serviced, all

Labels Bits

Function

C is set if the operation results in a carry during an addition operation or if a bor-

row does not take place during a subtraction operation; otherwise C is cleared. C

is also affected by a rotate through carry instruction.

0

1

C

AC is set if the operation results in a carry out of the low nibbles in addition or no

borrow from the high nibble into the low nibble in subtraction; otherwise AC is

cleared.

AC

Z is set if the result of an arithmetic or logic operation is zero; otherwise Z is

cleared.

2

3

4

5

Z

OV is set if the operation results in a carry into the highest-order bit but not a

carry out of the highest-order bit, or vice versa; otherwise OV is cleared.

OV

PD

TO

PD is cleared by system power-up or executing the "CLR WDT" instruction. PD

is set by executing the "HALT" instruction.

TO is cleared by system power-up or executing the "CLR WDT" or "HALT" in-

struction. TO is set by a WDT time-out.

6

7

Undefined, read as "0"

Undefined, read as "0"

¾

¾

Status register

10

February 25, 2000

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]