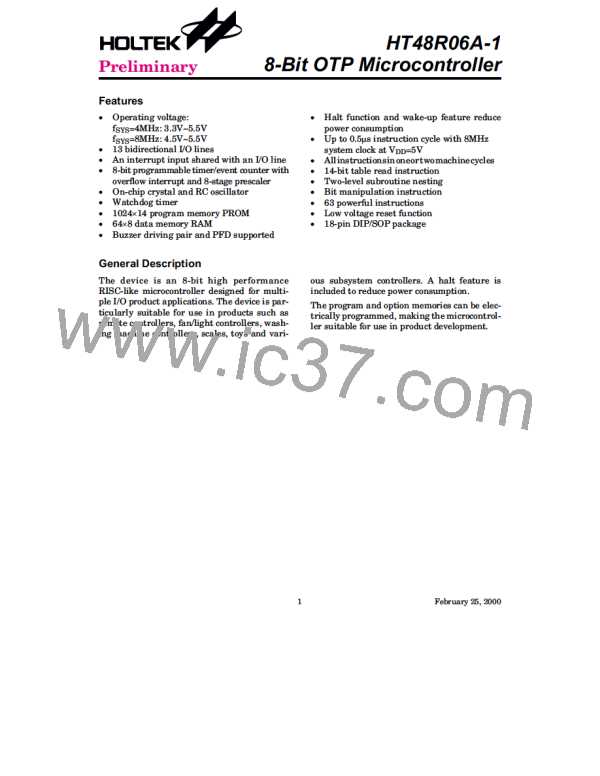

Preliminary

HT48R06A-1

All of the data memory areas can handle arith-

metic, logic, increment, decrement and rotate

operations directly. Except for some dedicated

bits, each bit in the data memory can be set and

reset by "SET [m].i" and "CLR [m].i". They are

also indirectly accessible through memory

pointer register (MP;01H).

I

n

d

i

r

e

c

t

A

d

d

r

e

s

s

i

n

g

R

e

g

i

s

t

e

r

0

0

0

0

0

0

0

0

0

0

0

1

2

3

4

5

6

7

8

9

H

H

H

H

H

H

H

H

H

H

M

P

A

C

C

P

C

L

T

B

L

P

T

B

L

H

Indirect addressing register

W

D

T

S

Location 00H is an indirect addressing register

that is not physically implemented. Any

read/write operation of [00H] accesses data mem-

ory pointed to by MP (01H). Reading location 00H

itself indirectly will return the result 00H. Writ-

ing indirectly results in no operation.

0

0

A

B

H

H

S

T

A

T

U

S

S

p

e

c

i

a

l

P

u

r

p

o

s

e

I

N

T

C

D

A

T

A

M

E

M

O

R

Y

0

0

C

D

H

H

T

M

R

0

E

H

T

M

R

C

0

F

H

H

H

H

H

H

H

H

H

H

H

1

1

1

1

1

1

1

1

1

1

0

1

2

3

4

5

6

7

8

9

The memory pointer register MP (01H) is a 7-bit

register. The bit 7 of MP is undefined and reading

will return the result 1 . Any writing operation

to MP will only transfer the lower 7-bit data to

MP.

P

P

A

B

P

P

A

B

C

C

P

C

Accumulator

P

C

C

The accumulator is closely related to ALU oper-

ations. It is also mapped to location 05H of the

data memory and can carry out immediate data

operations. The data movement between two

data memory locations must pass through the

accumulator.

:

U

n

u

s

e

d

1

1

A

B

H

H

R

e

a

d

a

s

"

0

0

"

1

1

C

D

H

H

1

E

H

1

F

H

Arithmetic and logic unit - ALU

2

0

H

This circuit performs 8-bit arithmetic and logic

operations. The ALU provides the following func-

tions:

3

F

H

H

4

0

G

e

A

n

e

r

a

l

P

u

r

p

o

s

e

D

T

A

M

E

M

O

R

Y

Arithmetic operations (ADD, ADC, SUB, SBC,

DAA)

(

6

4

B

y

t

e

s

)

7

F

H

·

Logic operations (AND, OR, XOR, CPL) Rota-

tion (RL, RR, RLC, RRC)

RAM mapping

·

·

Increment and Decrement (INC, DEC)

Branch decision (SZ, SNZ, SIZ, SDZ ....)

watchdog time-out flag (TO). It also records the

status information and controls the operation

sequence.

The ALU not only saves the results of a data op-

eration but also changes the status register.

With the exception of the TO and PD flags,

bits in the status register can be altered by

instructions like most other registers. Any

data written into the status register will not

change the TO or PD flag. In addition opera-

Status register - STATUS

This 8-bit register (0AH) contains the zero flag

(Z), carry flag (C), auxiliary carry flag (AC),

overflow flag (OV), power down flag (PD), and

9

February 25, 2000

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]