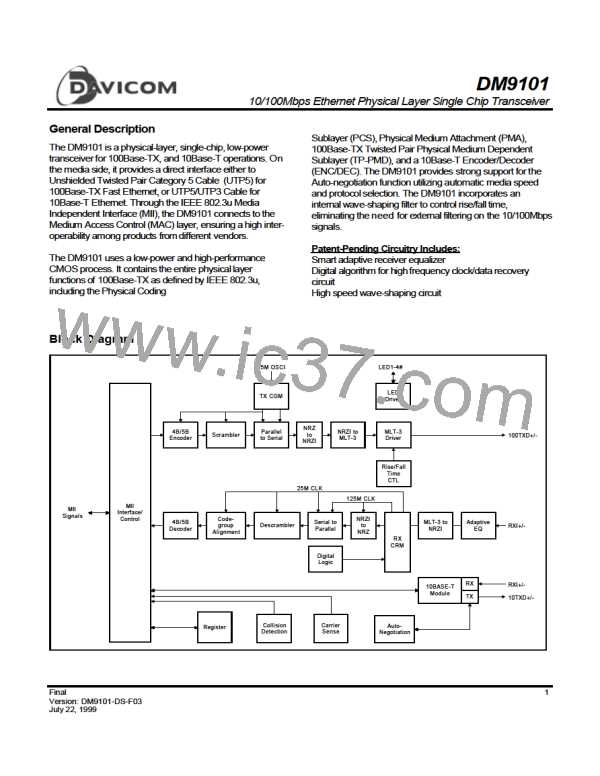

DM9101

10/100Mbps Ethernet Physical Layer Single Chip Transceiver

Pin Configuration: DM9101F QFP

AVCC

NC

1

80

79

RX_EN

RX_ER/RXD4

RX_DV

COL

2

NC

3

78

77

4

NC

NC

5

76

75

74

CRS

AGND

6

RX_CLK

DVCC

7

AVCC

RXI-

8

DGND

73

72

9

RXD0

RXI+

10

11

12

13

14

15

16

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

RXD1

AGND

AGND

10TXO-

10TXO+

AVCC

AVCC

AGND

AGND

NC

RXD2

RXD3

DVCC

DGND

MDIO

DM9101F

MDC

TX_CLK

TX_EN

DVCC

17

18

19

20

21

22

23

24

25

26

27

28

29

30

NC

DGND

TXD0

AVCC

AVCC

AGND

AGND

100TXO-

100TXO+

TXD1

TXD2

TXD3

TX_ER/TXD4

TXLED#

RXLED#

LINKLED#

DGND

AVCC

AVCC

OSCI/X1

X2

COLLED#

4

Final

Version: DM9101-DS-F03

July 22, 1999

ETC [ ETC ]

ETC [ ETC ]