DM9101

10/100Mbps Ethernet Physical Layer Single Chip Transceiver

Table of Contents

General Description................................................1

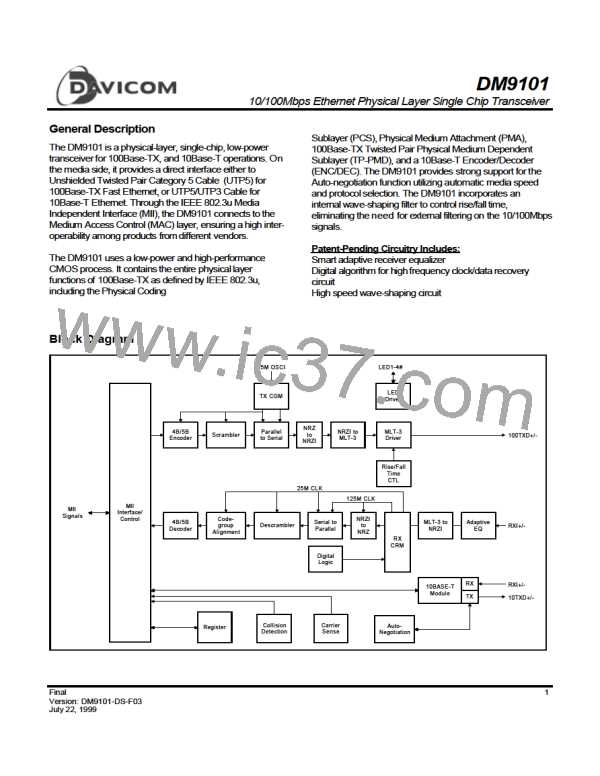

Block Diagram ........................................................1

Features.................................................................3

Pin Configuration: DM9101E LQFP.........................3

Pin Configuration: DM9101F QFP...........................4

Pin Description .......................................................5

- Register 2 ..........................................................23

PHY ID Identifier Register #2 (PHYIDR2)

- Register 3 ..........................................................24

Auto-negotiation Advertisement Register (ANAR)

- Register 4 ..........................................................24

Auto-negotiation Link Partner Ability Register

(ANLPAR) - Register 5 .........................................25

Auto-negotiation Expansion Register (ANER)

Functional Description

- Register 6 ..........................................................26

MII Interface ......................................................12

100Base-TX Operation......................................14

100Base-TX Transmit........................................14

100Base-TX Operation......................................15

4B5B Encoder ...................................................15

Scrambler..........................................................15

Parallel to Serial Converter................................15

NRZ to NRZI Encoder........................................15

MLT-3 Converter ...............................................15

MLT-3 Driver .....................................................15

4B5B Code Group .............................................16

100Base-TX Receiver........................................17

Signal Detect.....................................................17

Digital Adaptive Equalization..............................17

MLT-3 to NRZI Decoder.....................................17

Clock Recovery Module.....................................18

NRZI to NRZ .....................................................18

Serial to Parallel ................................................18

Descrambler......................................................18

Code Group Alignment ......................................18

4B5B Decoder...................................................18

10Base-T Operation ..........................................18

Collision Detection.............................................18

Carrier Sense ....................................................18

Auto-Negotiation................................................18

MII Serial Management......................................19

Serial Management Interface.............................19

Management Interface – Read Frame Structure.19

Management Interface – Write Frame Structure.19

DAVICOM Specified Configuration Register (DSCR)

- Register 16.........................................................26

DAVICOM Specified Configuration and Status

Register (DSCSR) - Register 17 ...........................28

10Base-T Configuration / Status (10BTSCRCSR)

- Register 18.........................................................29

Absolute Maximum Ratings..................................30

DC Electrical Characteristics ................................31

AC Characteristics................................................32

Timing Waveforms

MII-100Base-TX Transmit Timing Diagram ........33

MII-100Base-TX Receive Timing Diagram.........33

Auto-negotiation and Fast Link Pulse Timing.....34

MII-10Base-T Transmit Timing Diagram ............35

MII-10Base-T Receive Nibble Timing Diagram .. 35

10BASE-T SQE (Heartbeat) Timing Diagram.....36

10BASE-T Jab and Unjab Timing Diagram........36

MDIO Timing when OUTPUT by STA................37

MDIO Timing when OUTPUT by DM9101..........37

Magnetics Selection Guide ...................................38

Crystal Selection Guide........................................38

Application Circuit (for reference only) ..................40

Package Information.............................................41

Ordering Information.............................................42

Company Overview..............................................42

Contact Windows..................................................42

Register Description .............................................20

- Key To Default....................................................20

Basic Mode Control Register (BMCR)

- Register 0...........................................................21

Basic Mode Status Register (BMSR)

- Register 1...........................................................22

PHY ID Identifier Register #1 (PHYIDR1)

2

Final

Version: DM9101-DS-F03

July 22, 1999

ETC [ ETC ]

ETC [ ETC ]