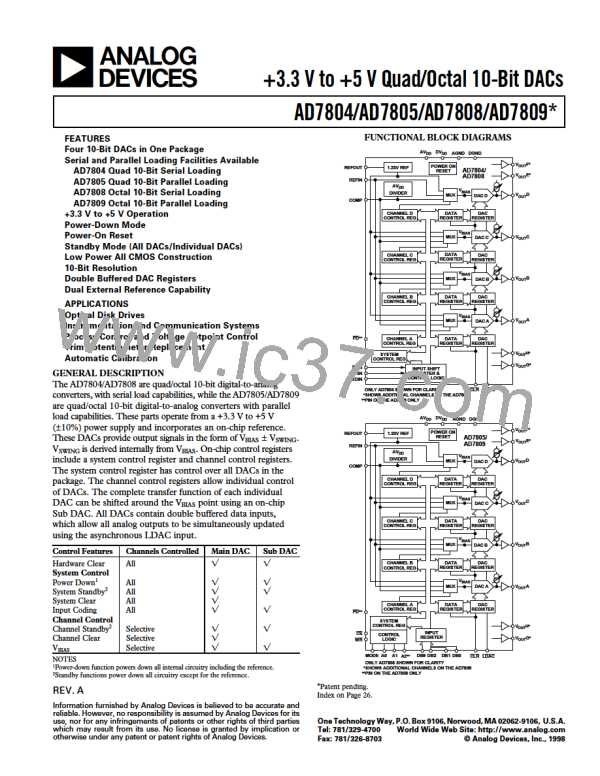

AD7804/AD7805/AD7808/AD7809

AD7804/AD7808 PIN FUNCTION DESCRIPTION

AD7804

Pin No.

AD7808

Pin No. Mnemonic

Description

1

2, 3

4

1, 6

2, 3

4

AGND

OUTB, VOUT

REFOUT

Ground reference point for analog circuitry.

Analog output voltage from the DACs.

Reference Output. This is a bandgap reference and is typically 1.23 V.

V

A

5

PD

Active low input used to put the part into low power mode reducing current consumption

to 1 µA.

7, 8

9

V

FSIN

OUTF, VOUT

E

Analog output voltages from the DACs.

5

6

Level-triggered control input (active low). This is the frame synchronization signal for the

input data. When FSIN goes low, it enables the input shift register and data is transferred

on the falling edges of CLKIN.

LDAC Input. When this digital input is taken low, all DAC registers are simultaneously

updated with the contents of the data registers. If LDAC is tied permanently low, or is

low on the sixteenth falling clock edge with timing similar to that of SDIN, an automatic

update will take place.

10

LDAC

7

11

SDIN

Serial Data Input. These devices accept a 16-bit word. Data is clocked into the input shift

register on the falling edge of CLKIN.

8

9

10

12

13

14

DGND

DVDD

CLKIN

Ground reference point for digital circuitry.

Digital Power Supply.

Clock Input. Data is clocked into the input shift register on the falling edges of CLKIN.

Duty Cycle should be between 40% and 60%.

11

15

CLR

Asynchronous CLR Input. When this input is taken low, all Main DAC outputs are

cleared either to VBIAS or to VBIAS/16 volts. All Sub DACs are also cleared and thus the

transfer function of the Main DAC will remain centered around the VBIAS point.

16

17, 18

20

NC

No Connect. This pin should be left open circuit.

Analog output voltages from the DACs.

This is an external reference input for the DACs. When this reference is selected for a

DAC in the control register, the analog output from the selected DAC swings around this

point.

VOUTH, VOUTG

REFIN

12

13

21

COMP

Compensation Pin. This pin provides an output from the internal VDD/2 divider and is

provided for ac bypass purposes only. This pin should be decoupled with 1 nF capacitors

to both AVDD and AGND. This pin can be overdriven with an external reference, thus

giving the facility for two external references on the part.

14, 15

16

22, 23

19, 24

V

AVDD

OUTD, VOUT

C

Analog output voltage from the DACs.

Analog Power Supply. +3.3 V to +5 V.

AD7808 PIN CONFIGURATION

AD7804 PIN CONFIGURATION

1

2

24

23

22

21

20

19

18

17

AGND

AV

V

DD

1

2

3

4

5

6

7

8

16 AV

DD

AGND

C

V

B

A

OUT

OUT

V

B

A

15

14

13

12

11

10

9

V

C

OUT

OUT

3

V

V

D

OUT

OUT

V

V

D

OUT

OUT

4

COMP

REFIN

REFOUT

AD7804

TOP VIEW

(Not to Scale)

REFOUT

COMP

REFIN

5

PD

AD7808

TOP VIEW

(Not to Scale)

FSIN

LDAC

SDIN

6

AV

DD

AGND

CLR

V

F

E

7

V

G

OUT

OUT

CLKIN

8

V

V

H

OUT

OUT

DGND

DV

DD

9

16 NC

15

FSIN

10

11

12

LDAC

SDIN

CLR

14

13

CLKIN

DGND

DV

DD

NC = NO CONNECT

REV. A

–7–

ETC [ ETC ]

ETC [ ETC ]