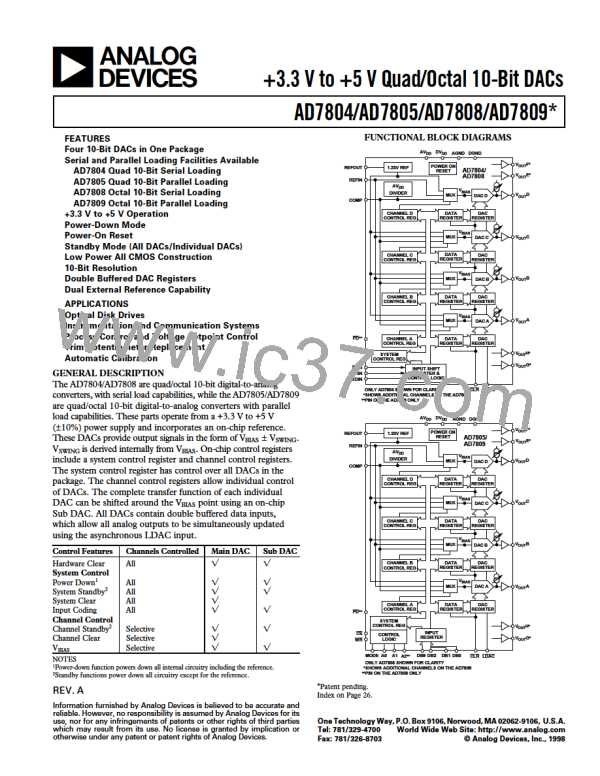

AD7804/AD7805/AD7808/AD7809

1

(V = 3.3 V ؎ 10% to 5 V ؎ 10%; AGND = DGND = 0 V; Reference =

DD

AD7804/AD7808 TIMING CHARACTERISTICS

Internal Reference. All specifications TMIN to TMAX unless otherwise noted.)

Limit at TMIN, TMAX

All Versions

Parameter

Units

Description

t1

t2

t3

t4

t5

t6

t6A

t7

100

40

40

30

30

5

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns max

ns min

ns min

ns min

CLKIN Cycle Time

CLKIN High Time

CLKIN Low Time

FSIN Setup Time

Data Setup Time

Data Hold Time

LDAC Hold Time

FSIN Hold Time

6

90

20

40

100

t8

t9

LDAC, CLR Pulsewidth

LDAC Setup Time

NOTES

1Sample tested during initial release and after any redesign or process change that may affect this parameter. All input signals are specified with tr = tf = 5 ns and

timed from a voltage of (VIL + VIH)/2.

Specifications subject to change without notice.

t1

CLKIN(I)

t2

t3

t4

t7

FSIN(I)

t5

t6

DB0

SDIN(I)

DB15

t6A

t5

1

LDAC

t9

2

LDAC

t8

t8

CLR

1

2

TIMING REQUIREMENTS FOR SYNCHRONOUS LDAC UPDATE OR LDAC MAY BE TIED PERMANENTLY LOW IF REQUIRED.

TIMING REQUIREMENTS FOR ASYNCHRONOUS LDAC UPDATE.

Figure 1. Timing Diagram for AD7804 and AD7808

–4–

REV. A

ETC [ ETC ]

ETC [ ETC ]