Product Preview

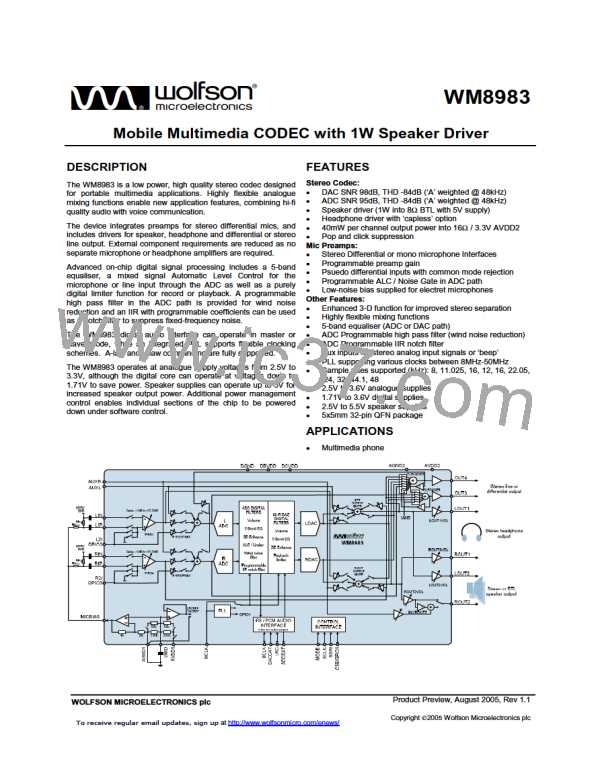

WM8983

In Right Justified mode, the LSB is available on the last rising edge of BCLK before a LRC transition.

All other bits are transmitted before (MSB first). Depending on word length, BCLK frequency and

sample rate, there may be unused BCLK cycles after each LRC transition.

Figure 36 Right Justified Audio Interface (assuming n-bit word length)

In I2S mode, the MSB is available on the second rising edge of BCLK following a LRC transition. The

other bits up to the LSB are then transmitted in order. Depending on word length, BCLK frequency

and sample rate, there may be unused BCLK cycles between the LSB of one sample and the MSB of

the next.

Figure 37 I2S Audio Interface (assuming n-bit word length)

In DSP/PCM mode, the left channel MSB is available on either the 1st (mode B) or 2nd (mode A)

rising edge of BCLK (selectable by LRP) following a rising edge of LRC. Right channel data

immediately follows left channel data. Depending on word length, BCLK frequency and sample rate,

there may be unused BCLK cycles between the LSB of the right channel data and the next sample.

In device master mode, the LRC output will resemble the LRC pulse shown in Figure 38 and Figure

39. In device slave mode, Figure 40 and Figure 41, it is possible to use any length of LRC pulse less

than 1/fs, providing the falling edge of the LRC pulse occurs greater than one BCLK period before the

rising edge of the next LRC pulse.

Figure 38 DSP/PCM Mode Audio Interface (mode A, LRP=0, Master)

PP Rev 1.1 August 2005

w

63

WOLFSON [ WOLFSON MICROELECTRONICS PLC ]

WOLFSON [ WOLFSON MICROELECTRONICS PLC ]