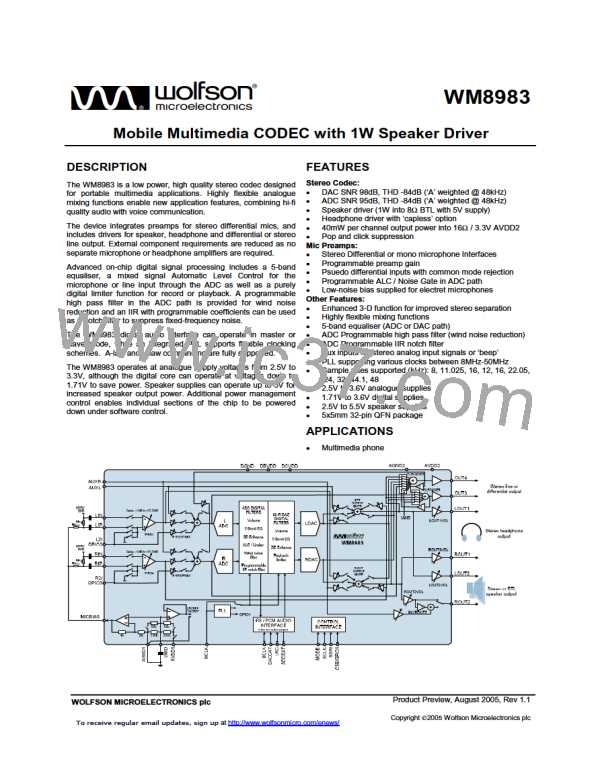

WM8983

Product Preview

REGISTER

ADDRESS

BIT

LABEL

DEFAULT

DESCRIPTION

R6

0

MS

0

Sets the chip to be master over LRC

and BCLK

Clock

Generation

Control

0=BCLK and LRC clock are inputs

(Slave mode)

1=BCLK and LRC clock are outputs

generated by the WM8983 (Master

mode)

4:2

BCLKDIV

000

Configures the BCLK and LRC output

frequency, for use when the chip is in

Master mode.

000=divide by 1 (BCLK=SYSCLK)

001=divide by 2 (BCLK=SYSCLK/2)

010=divide by 4

011=divide by 8

100=divide by 16

101=divide by 32

110=reserved

111=reserved

7:5

MCLKDIV

010

Sets the division for either the MCLK or

PLL clock output (selected by CLKSEL)

000=divide by 1

001=divide by 1.5

010=divide by 2 (LRC=SYSCLK/256)

011=divide by 3

100=divide by 4

101=divide by 6

110=divide by 8

111=divide by 12

8

CLKSEL

1

Controls the source of the clock for all

internal operation:

0=MCLK

1=PLL output

Table 47 Clock Control

SAMPLE

SYSCLK (MHZ)

(256FS CLOCK)

MCLKDIV

R6 [BIT 7:5]

SR

RATE (KHZ)

R7 [BIT3:1]

8

12.288

111 = divide by 12

110 = divide by 8

110 = divide by 8

101 = divide by 6

100 = divide by 4

100 = divide by 4

011 = divide by 3

010 = divide by 2

010 = divide by 2

010

11.025

12

11.2896

12.288

12.288

11.2896

12.288

12.288

11.2896

12.288

100

100

011

010

010

001

000

000

16

22.05

24

32

44.1

48

Table 48 Register Settings and Required SYSCLK for Common Sample Rates

PP Rev 1.1 August 2005

66

w

WOLFSON [ WOLFSON MICROELECTRONICS PLC ]

WOLFSON [ WOLFSON MICROELECTRONICS PLC ]