WED3DL644V

White Electronic Designs

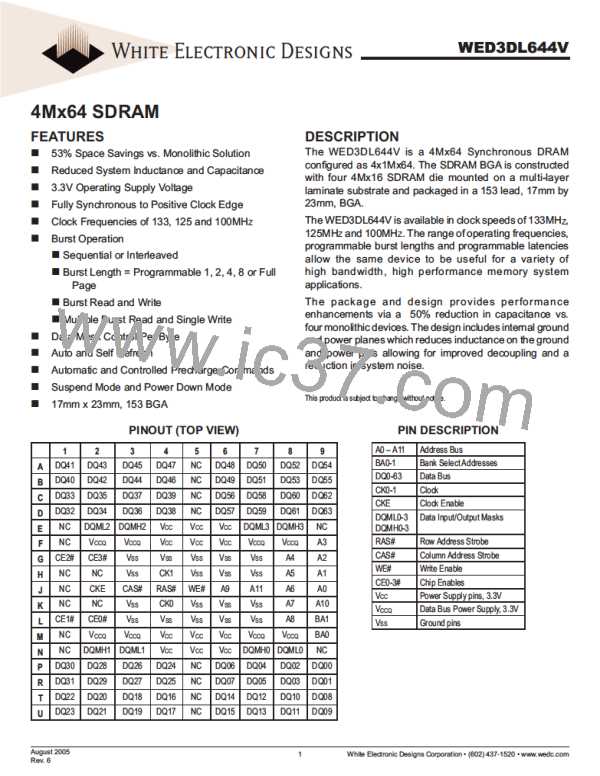

FIG. 5 READ & WRITE CYCLE AT SAME BANK @BURST LENGTH=4

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

CLOCK

HIGH

CKE

Note 1

tRC

CE#

tRCD

RAS#

Note 2

CAS#

ADDR

Ra

Ca0

Rb

Cb0

BA

A10/AP

CL = 2

Ra

Rb

tSHZ

Note 4

tRAC

tRDL

Note 3

tOH

tSAC

Qa0

Qa1

Qa2

Qa3

Db0

Db0

Db1

Db2

Db3

tSHZ Note 4

Qa3

DQ

tRAC

tRDL

tOH

Note 3

tSAC

CL = 3

Qa0

Qa1

Qa2

Db1

Db2

Db3

WE#

DQM

Row Active

(A-Bank)

Read

(A-Bank)

Precharge

(A-Bank)

Row Active

(A-Bank)

Write

(A-Bank)

Precharge

(A-Bank)

DON'T CARE

NOTES:

1.

2.

Minimum row cycle times are required to complete internal DRAM operation.

Row precharge can interrupt burst on any cycle. (CAS Latency - 1) number of valid output data is available after Row precharge. Last valid output will be Hi-Z(tSHZ) after the

clock.

Access time from Row active command. tCC *(tRCD + CAS latency - 1) + tSAC

3.

4.

.

Output will be Hi-Z after the end of burst (1, 2, 4, 8 & full page bit burst).

August 2005

Rev. 6

14

White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

WEDC [ WHITE ELECTRONIC DESIGNS CORPORATION ]

WEDC [ WHITE ELECTRONIC DESIGNS CORPORATION ]