DRV8301-Q1

www.ti.com

SLOS842 –SEPTEMBER 2013

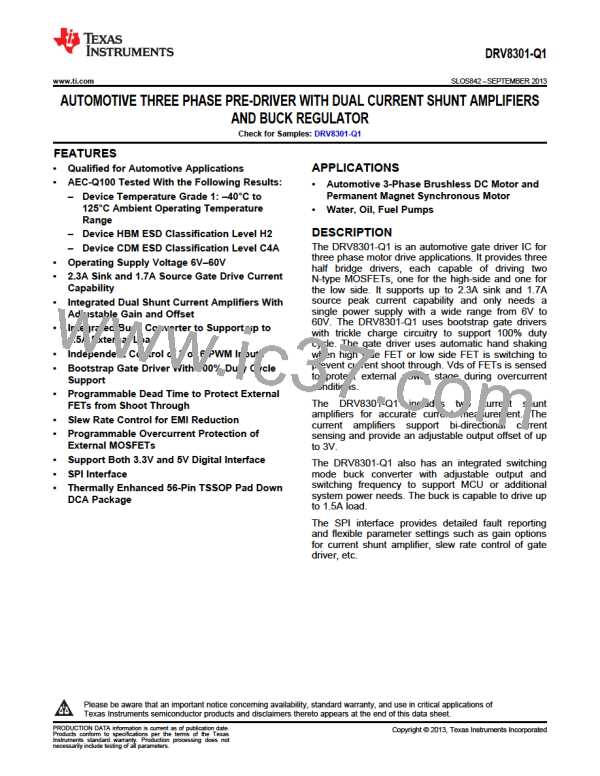

FUNCTION BLOCK DIAGRAM

PVDD1

CP2

OCTW

FAULT

Gate Driver

Control

&

Charge

Pump

Regulator

EN_GATE

DTC

OSC

CP1

Fault

Handling

(PVDD_UV,

CP_UV,

OTW, OTSD,

OC_LIMIT)

SCLK

SDI

GVDD

SDO

Trickle

Charge

PVDD1

SCS

VDD _SPI

BST_A

GH_A

Phase A

(repeated for B& C)

High Side

Motor

Gate Drive

Timing

_A

SH

INH_A

and

Control

Logic

GL _A

SL_A

_A

INL

Low Side

Gate Drive

PVDD2

Current

Sense

Amplifier1

SN1

SP1

VSENSE

BST_ BK

1

Rshunt

PGND

REF

PH

_

DC CAL

Offset

½ Vref

SN2

SP2

Current

Sense

Amplifier2

Buck

Converter

Power

Pad

_

EN BUCK

PWRGD

AVDD

_

SS TR

Offset

½ Vref

_

RT CLK

GND

COMP

DVDD

AGND

SO1

SO2

AGND GND PGND

Copyright © 2013, Texas Instruments Incorporated

Submit Documentation Feedback

5

Product Folder Links: DRV8301-Q1

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]