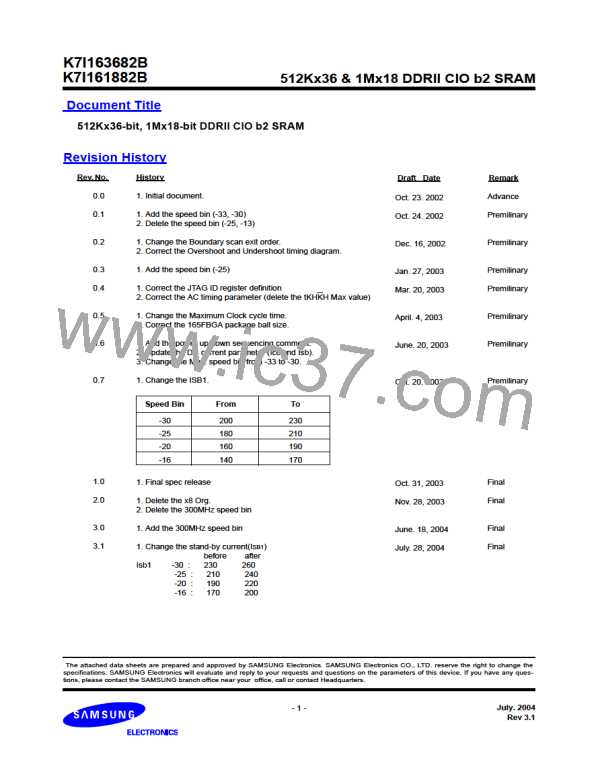

K7I163682B

K7I161882B

512Kx36 & 1Mx18 DDRII CIO b2 SRAM

JTAG DC OPERATING CONDITIONS

Parameter

Symbol

Min

1.7

Typ

Max

1.9

Unit

V

Note

Power Supply Voltage

VDD

VIH

1.8

Input High Level

1.3

-

-

-

-

VDD+0.3

0.5

V

Input Low Level

VIL

-0.3

1.4

V

Output High Voltage(IOH=-2mA)

Output Low Voltage(IOL=2mA)

VOH

VOL

VDD

V

VSS

0.4

V

Note: 1. The input level of SRAM pin is to follow the SRAM DC specification.

JTAG AC TEST CONDITIONS

Parameter

Symbol

VIH/VIL

TR/TF

Min

1.8/0.0

1.0/1.0

0.9

Unit

V

Note

Input High/Low Level

Input Rise/Fall Time

ns

V

Input and Output Timing Reference Level

Note: 1. See SRAM AC test output load on page 11.

1

JTAG AC Characteristics

Parameter

Symbol

Min

50

20

20

5

Max

Unit

Note

TCK Cycle Time

tCHCH

tCHCL

tCLCH

tMVCH

tCHMX

tDVCH

tCHDX

tSVCH

tCHSX

tCLQV

-

-

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

TCK High Pulse Width

TCK Low Pulse Width

TMS Input Setup Time

TMS Input Hold Time

TDI Input Setup Time

TDI Input Hold Time

-

-

5

-

5

-

5

-

SRAM Input Setup Time

SRAM Input Hold Time

Clock Low to Output Valid

5

-

5

-

0

10

JTAG TIMING DIAGRAM

TCK

tCHCH

tCHCL

tCLCH

tMVCH

tCHMX

TMS

TDI

tDVCH

tSVCH

tCHDX

tCHSX

PI

(SRAM)

tCLQV

TDO

July. 2004

Rev 3.1

- 16 -

SAMSUNG [ SAMSUNG ]

SAMSUNG [ SAMSUNG ]