RT8876A

Thermal Monitoring and Temperature Reporting

users have to set the TSEN voltage to be 1.515V when

VR temperature reaches 82°C and 1.845V when VR

temperature reaches 100°C. Detailed voltage setting

versus temperature variation is shown in Table 4. The

thermometer code is implemented in Temperature_Zone

register.

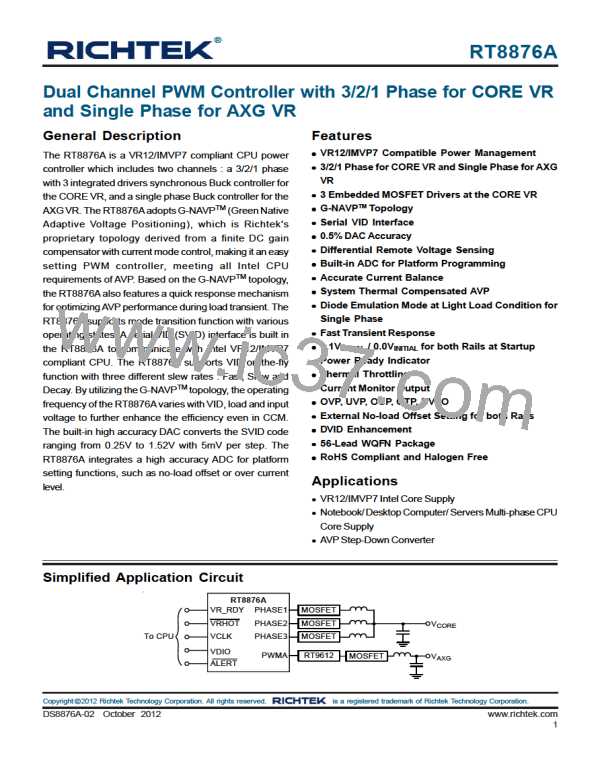

The CORE VR provides thermal monitoring function via

sensing TSEN pin voltage. Through the voltage divider

resistors, R1 and RNTC, the voltage of TSEN will be

proportional to VR temperature. When VR temperature

rises, TSEN voltage also rises. The ADC circuit of the

CORE VR monitors the voltage variation at the TSEN pin

from 1.46V to 1.845V with 55mV resolution. This voltage

is then decoded into digital format and stored into

Temperature_Zone register.

VCC5

R1

R

NTC

R2

R3

To meet Intel's VR12/IMVP7 specification, platform users

have to set the TSEN voltage to meet the temperature

variation of VR from 75% to 100% VR max temperature.

For example, if the VR max temperature is 100°C, platform

TSEN

Figure 14. CORE VR : Thermal Monitoring Circuit

Table 4. Temperature_Zone Register

SVID Thermal

Alert

Comparator Trip Points Temperatures Scaled to maximum = 100%

Voltage Represents Assert bit Minimum Level

VRHOT

b7

b6

b5

b4

b3

b2

b1

b0

100%

1.845V

97%

1.79V

94%

1.735V

91%

1.68V

88%

1.625V

85%

1.57V

82%

1.515V

75%

1.46V

voltage. In G-NAVPTM technology, the output voltage is

dependent on output current, and the current monitoring

function is achieved by this characteristic of output voltage.

Figure 15 shows the current monitoring setting principle.

The equivalent output current will be sensed from IMONFB

pin and mirrored to IMON pin. The resistor connected to

IMON pin determines voltage gain of the IMON output.

The current monitor indicator equation is shown as :

The VRHOT pin is an open-drain structure that sends out

active low VRHOT signal. When b6 of Temperature_Zone

register asserts to 1 (when TSEN voltage rises above

1.79V), theALERT signal will be asserted to low, which is

so-called SVIDthermal alert. In the mean time, the CORE

VR will assert bit 1 data to 1 in Status_1 register. The

ALERT assertion will be de-asserted when b5 of

Temperature_Zone register is de-asserted from 1 to 0

(which means TSENvoltage falls under 1.735V), and bit 1

of Status_1 register will also be cleared to 0. The bit 1

assertion of Status_1 is not latched and cannot be cleared

by GetReg command. When b7 of Temperature_Zone

register asserts to 1 (when TSEN voltage rises above

1.845V), the VRHOT signal will be asserted to low. The

VRHOT assertion will be de-asserted when b6 of

Temperature_Zone register is de-asserted from 1 to 0

(which means TSEN voltage falls under 1.79V). It is

typically recommended to connect a pull-up resistor from

the VRHOT pin to a voltage source.

I

x R

R

x R

LOAD

DROOP IMON

(21)

V

IMON

=

IMONFB

where ILOAD is the output load current, RDROOP is the

equivalent load line resistance, and RIMON and RIMONFB are

the current monitor current setting resistors. In VR12/

IMVP7 specification, the voltage signal of current

monitoring will be restricted by a maximum value. Platform

designers have to select RIMON to meet the maximum

voltage of IMON at full load. To find RIMON and RIMONFB

based on :

V

RIMON

IMON(MAX)

(22)

=

RIMONFB IMAX x RDROOP

Current Monitoring and Current Reporting

where the VIMON(MAX) is the maximum voltage at full load,

and IMAX is the full load current of VR.

The CORE VR provides current monitoring function via

sensing the voltage difference of IMONFB pin and output

Copyright 2012 Richtek Technology Corporation. All rights reserved.

©

is a registered trademark of Richtek Technology Corporation.

DS8876A-02 October 2012

www.richtek.com

37

RICHTEK [ RICHTEK TECHNOLOGY CORPORATION ]

RICHTEK [ RICHTEK TECHNOLOGY CORPORATION ]