MT9M021, MT9M031

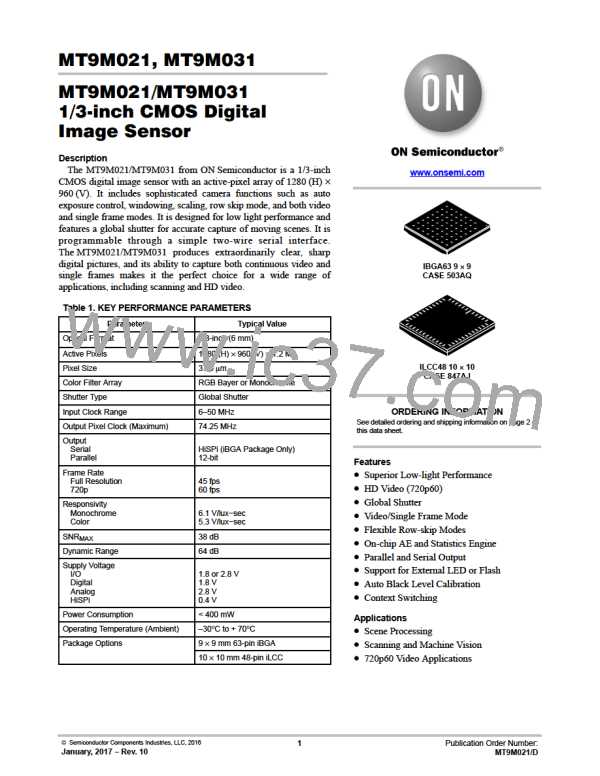

Table 4. PIN DESCRIPTIONS − 48-PIN ILCC PACKAGE, PARALLEL (continued)

Pin Number

10

11

Name

Type

Output

Output

Power

Output

Power

Input

Description

D

10

Parallel pixel data output

Parallel pixel data output (MSB)

I/O supply power

OUT

OUT

D

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

V

DD

_IO

PIXCLK

Pixel clock out. D

is valid on rising edge of this clock

OUT

V

DD

Digital power

S

CLK

Two-Wire Serial clock input

Two-Wire Serial data I/O

S

DATA

I/O

RESET_BAR

_IO

Input

Asynchronous reset (active LOW). All settings are restored to factory default

I/O supply power

V

DD

Power

Power

V

DD

Digital power

NC

NC

No connection

No connection

STANDBY

OE_BAR

Input

Input

Standby-mode enable pin (active HIGH)

Output enable (active LOW)

Two-Wire Serial address select

S

ADDR

Input

TEST

FLASH

Input

Manufacturing test enable pin (connect to D

)

GND

Output

Input

Flash output control

TRIGGER

FRAME_VALID

LINE_VALID

Exposure synchronization input

Output

Output

Power

N/A

Asserted when D

Asserted when D

Digital ground

frame data is valid

line data is valid

OUT

OUT

D

GND

Reserved

Reserved

Reserved

Reserved (do not connect)

Reserved (do not connect)

Reserved (do not connect)

Analog power

N/A

N/A

V

AA

Power

Power

Power

Power

Power

Power

Power

A

GND

Analog ground

V

AA

Analog power

V

_PIX

_PIX

Pixel power

AA

V

AA

Pixel power

A

GND

Analog ground

V

AA

Analog power

NC

NC

NC

No connection

No connection

No connection

D

Power

Output

Output

Output

Output

Digital ground

GND

D

D

D

D

0

Parallel pixel data output (LSB)

Parallel pixel data output

Parallel pixel data output

Parallel pixel data output

OUT

OUT

OUT

OUT

1

2

3

www.onsemi.com

9

ONSEMI [ ONSEMI ]

ONSEMI [ ONSEMI ]