MT9M021, MT9M031

1

2

3

4

5

6

7

8

A

B

SLVS0N

SLVS0P

SLVS1N

SLVS1P

V

V

STANDBY

DD

DD

V

_PLL

SLVSCN

SLVSCP

SLVS3N

SLVS2N

SLVS3P

SLVS2P

V

DD

V

V

AA

DD

AA

C

D

E

EXTCLK

V

DD

_SLVS

D

D

D

V

V

A

GND

A

GND

GND

GND

DD

S

S

CLK

S

DATA

D

V

_PIX

V

AA

_PIX

ADDR

GND

DD

AA

LINE_

VALID

FRAME_

VALID

PIXCLK

FLASH

V

V

V

V

_IO

_IO

_IO

_IO

RESERVED RESERVED

GND

GND

GND

DD

DD

DD

F

G

H

D

D

D

8

4

0

D

D

D

9

5

1

D

10

OUT

D 11

OUT

D

D

D

TEST

RESERVED

OE_BAR

OUT

OUT

D

6

D

7

3

TRIGGER

OUT

OUT

OUT

OUT

OUT

RESET_

BAR

D

2

D

V

_IO

OUT

OUT

OUT

GND

DD

DD

Top View

(Ball Down)

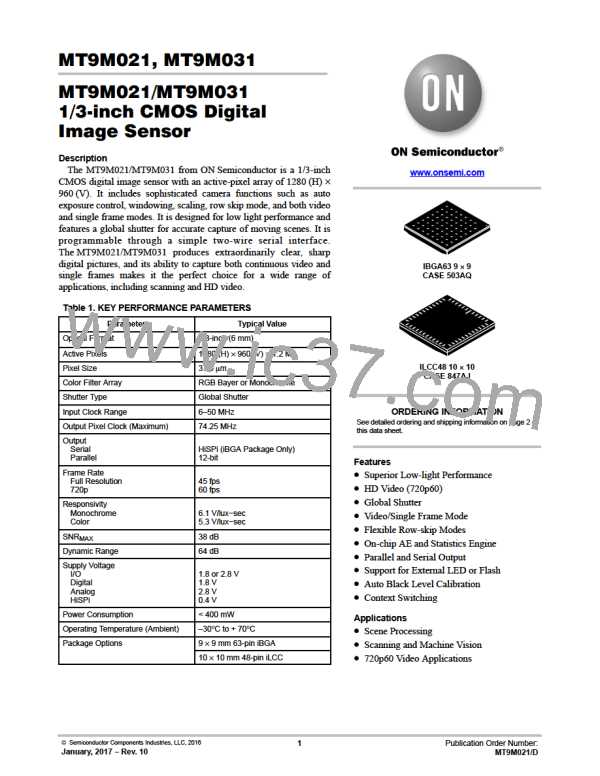

Figure 4. 9 y 9 mm 63-ball iBGA Package

Table 3. PIN DESCRIPTIONS − 63-BALL IBGA PACKAGE

Name

iBGA Pin

A2

Type

Output

Output

Output

Output

Input

Description

HiSPi serial data, lane 0, differential N

HiSPi serial data, lane 0, differential P

HiSPi serial data, lane 1, differential N

HiSPi serial data, lane 1, differential P

Standby-mode enable pin (active HIGH)

PLL power

SLVS0_N

SLVS0_P

SLVS1_N

SLVS1_P

STANDBY

A3

A4

A5

A8

V

_PLL

B1

Power

Output

DD

SLVSC_N

B2

HiSPi serial DDR clock differential N

www.onsemi.com

6

ONSEMI [ ONSEMI ]

ONSEMI [ ONSEMI ]