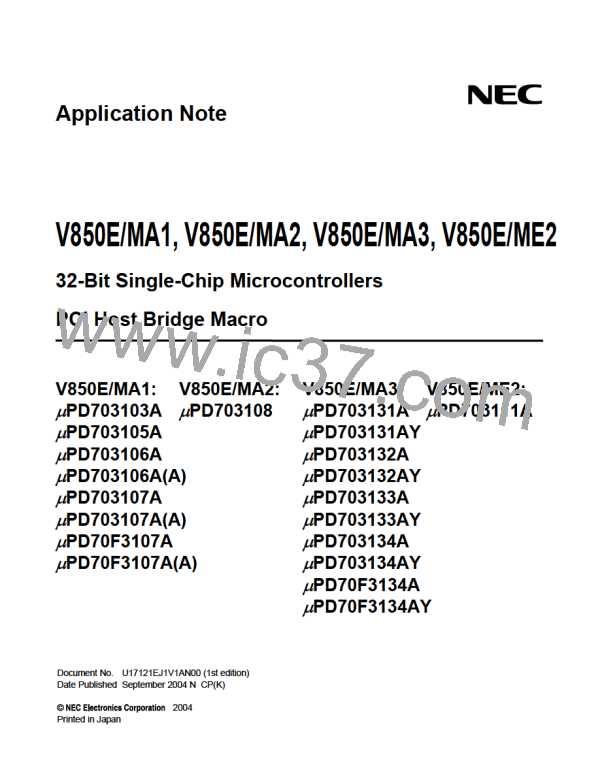

CHAPTER 3 SPECIFICATIONS OF PCI HOST BRIDGE MACRO

3.4.8 SYSTEM_MEM_BASE register

When the main memory is accessed from the PCI device by setting the SYSTEM_MEM_BASE register and

SYSTEM_MEM_RANGE register, the register responds to an access of a matching address.

After reset: 00000000H

31

R/W

Offset address: 40H

16 15

0

0

0

S_BASE

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit Name

S_BASE

R/W

Function

R/W Sets the higher 16 bits (bits 16 to 31) of the base address on the PCI bus memory space in which

the main memory (SDRAM) is mapped.

3.4.9 SYSTEM_MEM_RANGE register

After reset: 0000FFFFH

31

R/W

Offset address: 44H

16 15

1

0

1

S_RANGE

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Bit Name

R/W

Function

S_RANGE

R/W Sets the range of the PCI bus memory space in which the main memory (SDRAM) is mapped.

It can be set in 64 KB units.

0000H: 64 KB

0001H: 128 KB

:

000FH: 1 MB

:

00FFH: 16 MB

:

0FFFH: 256 MB

:

FFFFH: 4 GB

41

Application Note U17121EJ1V1AN

NEC [ NEC ]

NEC [ NEC ]