ADVANCE

4 MEG x 8, 4 MEG x 9, 2 MEG x 18, 1 MEG x 36

1.8V VDD, HSTL, QDRIIb2 SRAM

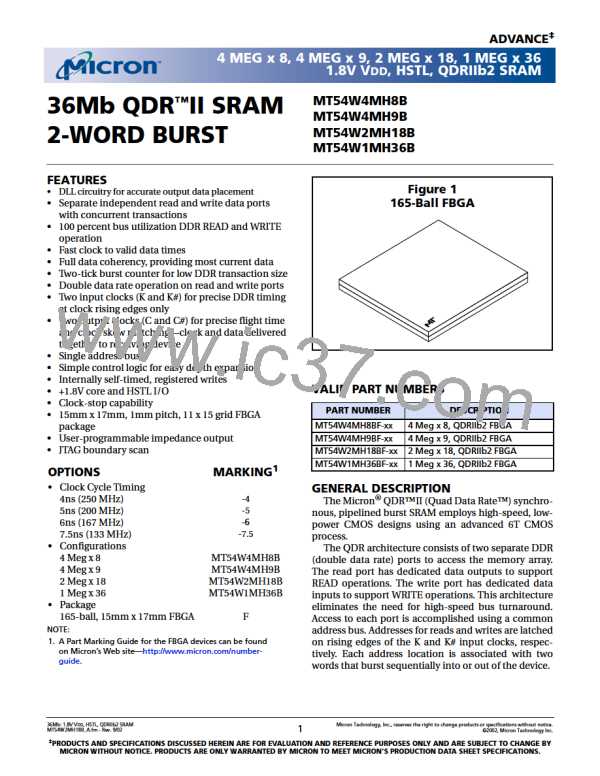

4 MEG x 9 BALL ASSIGNMENT (TOP VIEW)

165-BALL FBGA

1

2

3

SA

4

5

6

7

8

9

SA

10

SA

11

CQ

Q4

D4

NC

Q3

NC

NC

ZQ

D2

NC

Q1

D1

NC

Q0

TDI

VSS/SA1

NC

NC/SA2

BW0#4

SA

A

B

C

D

E

CQ#

NC

W#

NC

K#

K

R#

NC/SA3

SA

NC

NC

NC

Q5

NC

Q6

VDDQ

NC

NC

D7

SA

SA

NC

NC

NC

NC

NC

NC

VDDQ

NC

NC

NC

NC

NC

NC

SA

NC

NC

NC

D3

NC

NC

VSS

SA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SA

C

VSS

NC

D5

NC

NC

D6

VSS

VSS

VSS

VSS

NC

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

F

NC

VDD

VDD

VDD

VDD

VDD

VSS

VDD

VDD

VDD

VDD

VDD

VSS

NC

NC

VREF

Q2

NC

NC

NC

NC

D0

G

H

J

NC

DLL#

NC

VREF

NC

NC

Q7

NC

D8

K

L

NC

NC

M

N

P

NC

NC

NC

Q8

SA

VSS

VSS

NC

VSS

SA

SA

VSS

NC

NC

TCK

SA

SA

SA

SA

R

TDO

SA

SA

C#

SA

SA

TMS

NOTE:

1. Expansion address: 2A for 72Mb

2. Expansion address: 7A for 144Mb

3. Expansion address: 5B for 288Mb

4. BW0# controls writes to D0:D8

36Mb: 1.8V VDD, HSTL, QDRIIb2 SRAM

MT54W2MH18B_A.fm - Rev 9/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology Inc.

6

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]