64Mb : x4, x8, x16

SDRAM

1

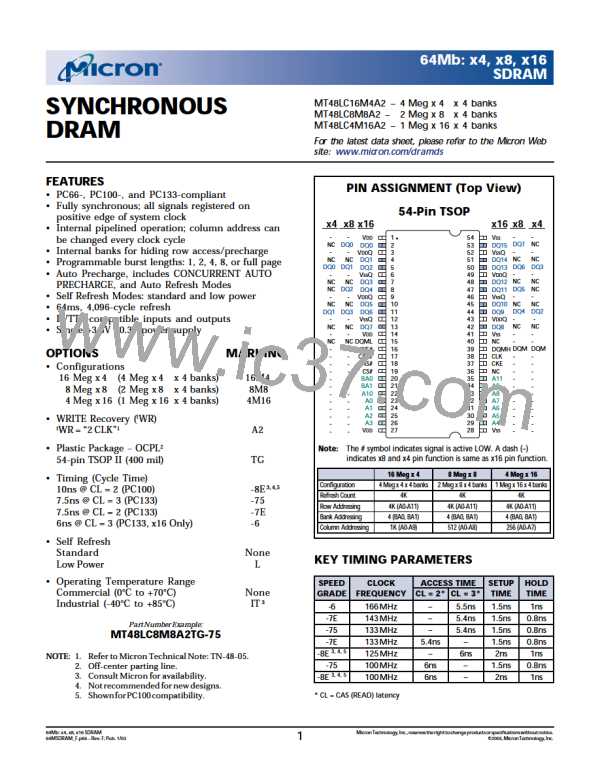

INITIALIZE AND LOAD MODE REGISTER

T0

T1

Tn + 1

To + 1

CL

Tp + 1

Tp + 2

Tp + 3

( (

) )

( (

) )

( (

) )

t

t

CK

CLK

CKE

((

))

t

( (

) )

( (

) )

( (

) )

CH

t

t

CKH

CKS

((

))

((

))

( (

) )

( (

) )

( (

) )

( (

) )

t

t

t

t

t

t

CMS CMH

CMS CMH

CMS CMH

( (

) )

( (

) )

( (

) )

( (

) )

AUTO

REFRESH

AUTO

REFRESH

LOAD MODE

REGISTER

COMMAND

NOP

PRECHARGE

NOP

NOP

NOP

NOP

NOP

ACTIVE

( (

) )

( (

) )

( (

) )

( (

) )

( (

) )

( (

) )

( (

) )

( (

) )

DQM /

DQML, DQMH

( (

) )

( (

) )

( (

) )

( (

) )

t

t

t

AH

AS

( (

) )

( (

) )

( (

) )

( (

) )

A0-A9, A11

A10

CODE

ROW

ROW

BANK

( (

) )

( (

) )

( (

) )

( (

) )

t

AS

AH

( (

) )

( (

) )

ALL BANKS

( (

) )

( (

) )

CODE

( (

) )

( (

) )

( (

) )

( (

) )

SINGLE BANK

( (

) )

( (

) )

( (

) )

( (

) )

ALL

BANKS

BA0, BA1

DQ

( (

) )

( (

) )

( (

) )

( (

) )

High-Z

((

))

((

))

T = 100µs

MIN

t

t

t

t

MRD

RP

RFC

RFC

Power-up:

2, 3, 4

Program Mode Register

AUTO REFRESH

VDD and

AUTO REFRESH

Precharge

all banks

CLK stable

DON’T CARE

TIMING PARAMETERS

-6

-7 E

-7 5

-8 E

-6

-7 E

-7 5

-8 E

SYMBOL* MIN MAX MIN MAX MIN MAX MIN MAX UNITS

SYMBOL* MIN MAX MIN MAX MIN MAX MIN MAX UNITS

t

t

AH

1

1.5

2.5

2.5

6

0.8

1.5

2.5

2.5

7

0.8

1.5

2.5

2.5

7.5

10

1

2

ns

ns

ns

ns

ns

ns

ns

CKS

1.5

1

1.5

0.8

1.5

2

1.5

0.8

1.5

2

2

1

ns

ns

ns

CK

ns

ns

t

t

t

t

t

t

t

t

t

t

t

AS

CMH

CMS

CH

3

1.5

2

2

3

t

CL

3

MRD

RFC

RP

2

CK(3)

CK(2)

CKH

8

60

18

66

15

66

20

70

20

–

7.5

0.8

10

1

1

0.8

*CAS latency indicated in parentheses.

NOTE: 1. If CS# is HIGH at clock HIGH time, all commands applied are NOP.

2. The mode register may be loaded prior to the AUTO REFRESH cycles if desired.

3. JEDEC and PC100 specify three clocks.

4. Outputs are guaranteed High-Z after command is issued.

64Mb: x4, x8, x16 SDRAM

64MSDRAM_F.p65 – Rev. F; Pub. 1/03

Micron Technology, Inc., reservesthe right to change productsor specificationswithout notice.

©2003, Micron Technology, Inc.

36

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]