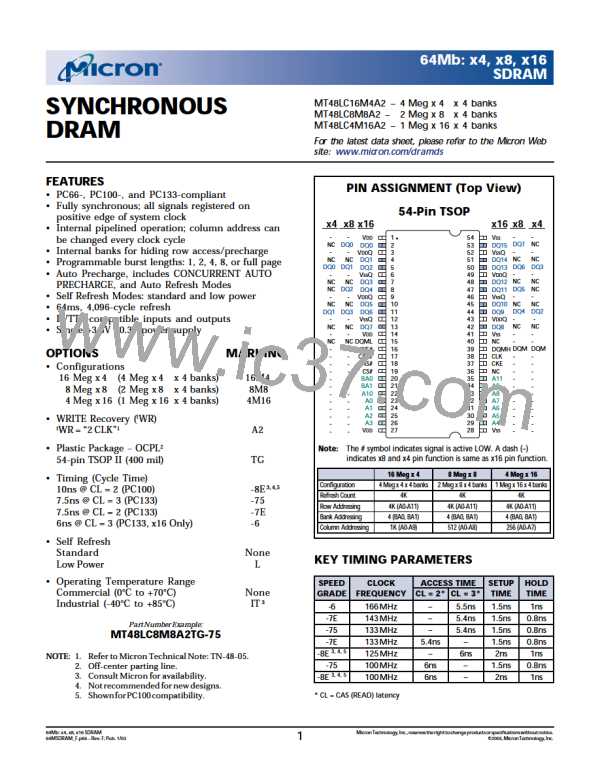

64Mb : x4, x8, x16

SDRAM

CAPACITANCE

(Note: 2; notes appear on page 35)

PARAMETER

SYMBOL M IN M AX UNITS NOTES

Input Capacitance: CLK

CI1

CI2

CIO

2.5

2.5

4.0

3.5

3.8

6.0

pF

pF

pF

29

30

31

Input Capacitance: All other input-only pins

Input/Output Capacitance: DQs

ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

(Notes: 5, 6, 8, 9, 11; notes appear on page 35); VDD, VDDQ = +3.3V ±0.3V

ACCHARACTERISTICS

PARAMETER

-6

-7E

MAX MIN

-75

MAX

-8E

MIN

SYMBOL MIN

MAX

5.5

–

MIN

MAX UNITS NOTES

t

Access time from CLK (pos. edge)

CL = 3

CL = 2

AC(3)

5.4

5.4

5.4

6

6

6

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

27

t

AC(2)

t

Address hold time

Address setup time

CLKhigh-levelwidth

CLK low-level width

Clock cycle time

AH

1

1.5

2.5

2.5

6

0.8

1.5

2.5

2.5

7

0.8

1.5

2.5

2.5

7.5

10

1

2

t

AS

CH

t

3

t

CL

3

t

t

CL = 3

CL = 2

CK(3)

CK(2)

8

23

23

–

7.5

0.8

1.5

0.8

1.5

0.8

1.5

10

1

t

CKE hold time

CKE setup time

CKH

1

0.8

1.5

0.8

1.5

0.8

1.5

t

CKS

1.5

1

2

t

CS#, RAS#, CAS#, WE#, DQM hold time

CS#, RAS#, CAS#, WE#, DQM setup time

Data-in hold time

CMH

1

t

CMS

1.5

1

2

t

DH

1

t

Data-in setup time

DS

1.5

2

t

t

Data-out high-impedance time

CL = 3

CL = 2

HZ(3)

HZ(2)

5.5

–

5.4

5.4

5.4

6

6

6

10

10

t

Data-out low-impedance time

Data-out hold time (load)

LZ

1

2

1

3

1

3

1

3

t

OH

t

Data-out hold time (no load)

ACTIVEto PRECHARGEcommand

ACTIVEto ACTIVEcommand period

ACTIVE to READ or WRITE delay

Refresh period (4,096 rows)

AUTO REFRESHperiod

OH

1.8

42

60

18

1.8

37

60

15

1.8

1.8

50

70

20

28

N

t

RAS

120,000

64

120,000 44

120,000

64

120,000 ns

t

RC

66

ns

ns

t

RCD

20

t

REF

RFC

64

66

20

15

64

ms

ns

ns

ns

ns

–

t

60

18

66

15

70

20

t

PRECHARGEcommand period

RP

t

ACTIVE bank a to ACTIVE bank b command

Transition time

RRD

12

14

20

t

T

0.3

1.2

0.3

1.2

0.3

1.2

0.3

1.2

7

t

WRITE recovery time

WR

1 CLK +

6ns

1 CLK +

7ns

1 CLK +

7.5ns

15

1 CLK +

7ns

24

12

14

15

ns

ns

25

20

t

Exit SELF REFRESH to ACTIVE command

XSR

70

67

75

80

64Mb: x4, x8, x16 SDRAM

64MSDRAM_F.p65 – Rev. F; Pub. 1/03

Micron Technology, Inc., reservesthe right to change productsor specificationswithout notice.

©2003, Micron Technology, Inc.

33

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]