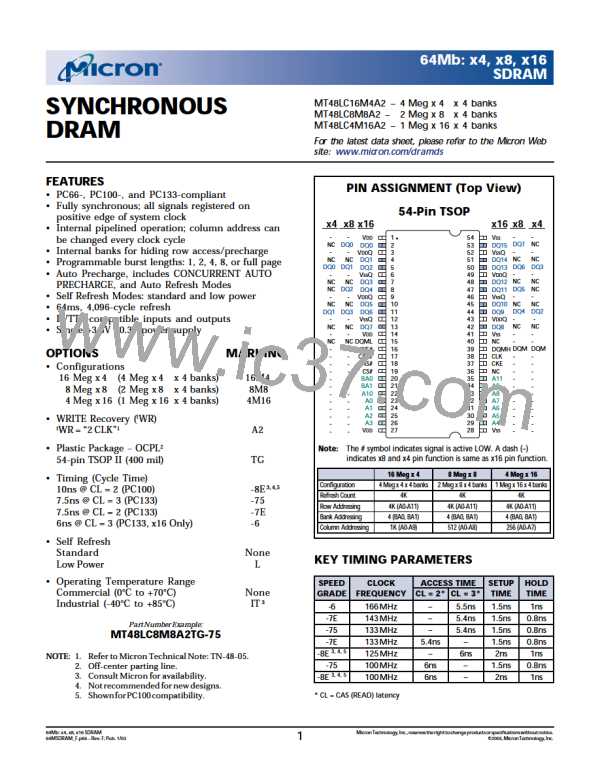

64Mb : x4, x8, x16

SDRAM

WRITE with Auto Precharge

3. In terru p ted by a READ (with or with ou t au to

precharge): A READ to bank m will interrupt a WRITE

on bank n when registered, with the data-out appear-

ing CAS latency later. The PRECHARGE to bank n will

4. In terru p ted by a WRITE (with or with ou t au to

precharge): AWRITE to bank m will interrupt a WRITE

on bank n when registered. The PRECHARGE to bank

t

n will begin after tWR is met, where WR begins when

t

t

begin after WR is met, where WR begins when the

READ to bank m is registered. The last valid WRITE to

bank n will be data-in registered one clock prior to the

READ to bank m (Figure 26).

the WRITE to bank m is registered. The last valid data

WRITE to bank n will be data registered one clock prior

to a WRITE to bank m (Figure 27).

Fig u re 26

WRITE Wit h Au t o Pre ch a rg e In t e rru p t e d b y a READ

T0

T1

T2

T3

T4

T5

T6

T7

CLK

WRITE - AP

BANK n

READ - AP

BANK m

NOP

NOP

NOP

NOP

NOP

NOP

COMMAND

Page Active

WRITE with Burst of 4

Interrupt Burst, Write-Back

Precharge

BANK n

t

RP - BANK n

t

WR - BANK n

Internal

States

t

RP - BANK m

Page Active

READ with Burst of 4

BANK m

BANK n,

COL a

BANK m,

COL d

ADDRESS

DQ

DIN

D

a + 1

IN

DOUT

DOUT

a

d

d + 1

CAS Latency = 3 (BANK m)

TRANSITIONING DATA

DON’T CARE

NOTE: 1. DQM is LOW.

Fig u re 27

WRITE Wit h Au t o Pre ch a rg e In t e rru p t e d b y a WRITE

T0

T1

T2

T3

T4

T5

T6

T7

CLK

WRITE - AP

BANK n

WRITE - AP

BANK m

NOP

NOP

NOP

NOP

NOP

NOP

COMMAND

Page Active

WRITE with Burst of 4

Interrupt Burst, Write-Back

Precharge

BANK n

t

RP - BANK n

t

WR - BANK n

Internal

States

t

WR - BANK m

Write-Back

Page Active

WRITE with Burst of 4

BANK m

BANK n,

COL a

BANK m,

COL d

ADDRESS

DQ

DIN

D

a + 1

IN

D

a + 2

IN

DIN

DIN

DIN

DIN

a

d

d + 1

d + 2

d + 3

TRANSITIONING DATA

DON’T CARE

NOTE: 1. DQM is LOW.

64Mb: x4, x8, x16 SDRAM

64MSDRAM_F.p65 – Rev. F; Pub. 1/03

Micron Technology, Inc., reservesthe right to change productsor specificationswithout notice.

©2003, Micron Technology, Inc.

26

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]