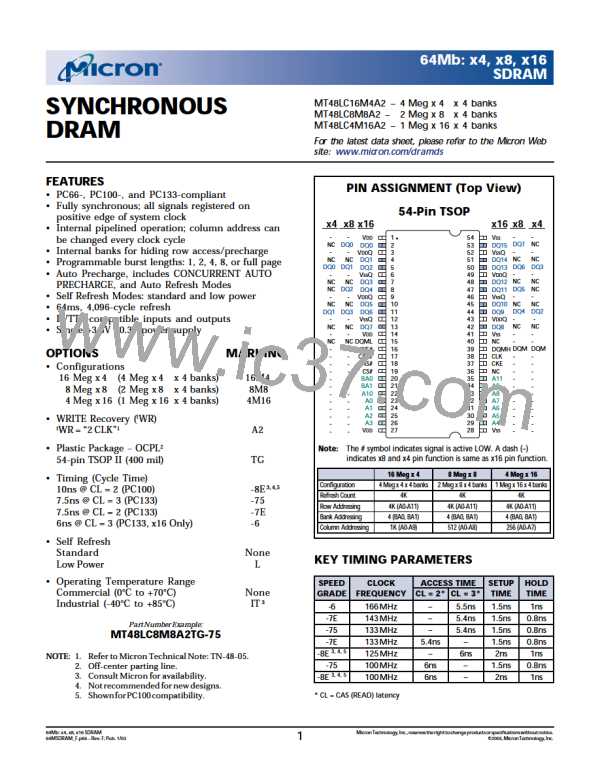

64Mb : x4, x8, x16

SDRAM

TRUTH TABLE 2 – CKE

(Notes: 1-4)

CKEn -1 CKEn

CURRENT STATE

COMMANDn

ACTIONn

NOTES

L

L

L

H

L

Power-Down

Self Refresh

X

Maintain Power-Down

Maintain Self Refresh

Maintain Clock Suspend

Exit Power-Down

X

Clock Suspend

Power-Down

Self Refresh

X

COMMAND INHIBIT or NOP

COMMAND INHIBIT or NOP

X

5

6

7

Exit Self Refresh

Clock Suspend

All Banks Idle

All Banks Idle

Reading or Writing

Exit Clock Suspend

Power-Down Entry

Self Refresh Entry

H

COMMAND INHIBIT or NOP

AUTO REFRESH

VALID

Clock Suspend Entry

H

H

See Truth Table 3

NOTE: 1. CKE is the logic state of CKE at clock edge n; CKE was the state of CKE at the previous clock edge.

n

n-1

2. Current state is the state of the SDRAM immediately prior to clock edge n.

3. COMMAND is the command registered at clock edge n, and ACTION is a result of COMMAND .

n

n

n

4. All states and sequences not shown are illegal or reserved.

5. Exiting power-down at clock edge n will put the device in the all banks idle state in time for clock edge n + 1 (provided

t

that CKS is met).

t

6. Exiting self refresh at clock edge n will put the device in the all banks idle state once XSR is met. COMMAND INHIBIT

t

or NOP commands should be issued on any clock edges occurring during the XSR period. A minimum of two NOP

commands must be provided during XSR period.

t

7. After exiting clock suspend at clock edge n, the device will resume operation and recognize the next command at clock

edge n + 1.

64Mb: x4, x8, x16 SDRAM

64MSDRAM_F.p65 – Rev. F; Pub. 1/03

Micron Technology, Inc., reservesthe right to change productsor specificationswithout notice.

©2003, Micron Technology, Inc.

27

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]