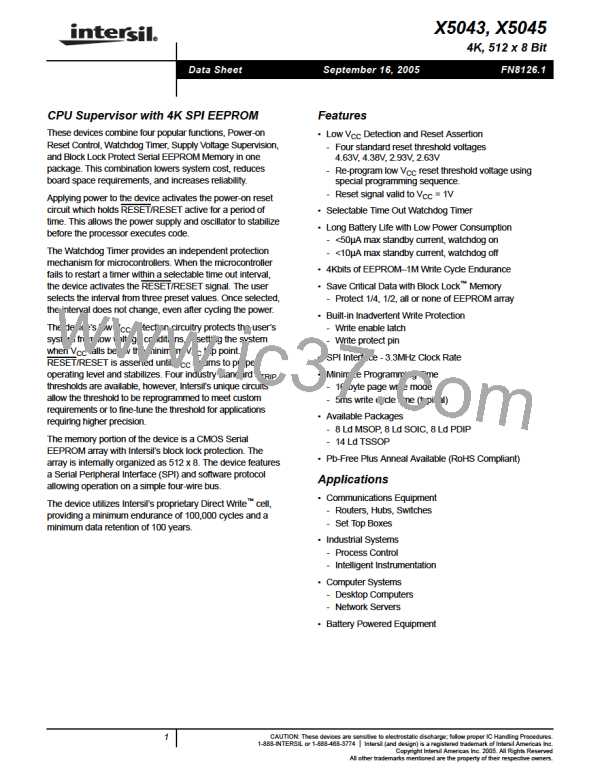

X5043, X5045

TABLE 2. DEVICE PROTECT MATRIX

MEMORY BLOCK

STATUS REGISTER

(BL0, BL1, WD0, WD1)

Protected

WREN CMD

(WEL)

DEVICE PIN (WP)

PROTECTED AREA

UNPROTECTED AREA

0

x

1

x

0

1

Protected

Protected

Protected

Protected

Protected

Writable

Protected

Writable

CS

SCK

SI

0

1

2

3

4

5

6

7

8

9 10 11 12 13 14

15

Instruction

Data Out

High Impedance

SO

7

6

5

4

3

2

1

0

MSB

FIGURE 6. READ STATUS REGISTER SEQUENCE

CS

0

1

2

3

4

5

6

7

8

7

9

6

10 11 12 13 14 15

SCK

Data Byte

Instruction

5

4

3

2

1

0

SI

High Impedance

FIGURE 7. WRITE STATUS REGISTER SEQUENCE

SO

FN8126.1

September 16, 2005

10

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]