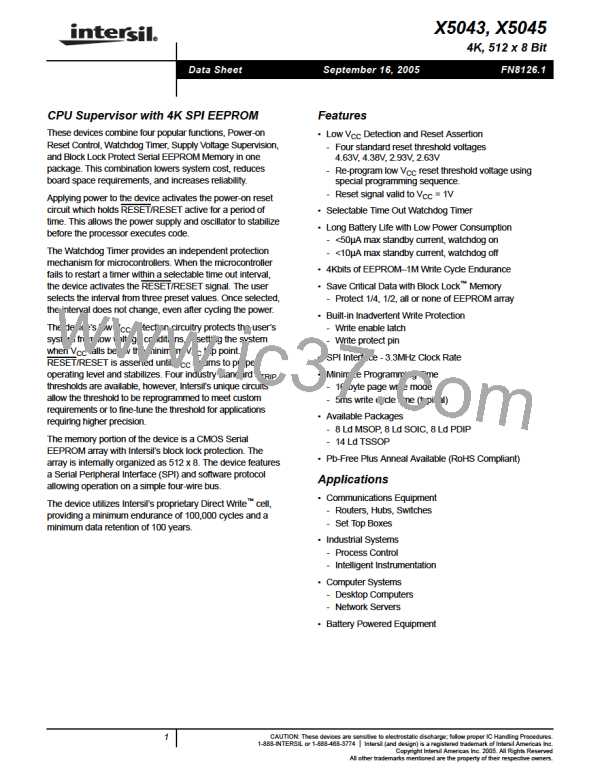

X5043, X5045

CS

0

1

2

3

4

8

5

6

7

8

9

10

12 13 14 15 16 17 18 19 20 21 22 23

SCK

Instruction

8 Bit Address

Data Byte 1

7

6

5

3

2

1

0

7

6

5

4

3

2

1

0

SI

9th Bit of Address

CS

24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39

SCK

Data Byte 2

Data Byte 3

Data Byte N

SI

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

6

5

4

3

2

1

0

FIGURE 9. WRITE MEMORY SEQUENCE

Operational Notes

The device powers-up in the following state:

1. The device is in the low power standby state.

2. A HIGH to LOW transition on CS is required to enter an

active state and receive an instruction.

3. SO pin is high impedance.

4. The Write Enable Latch is reset.

5. The Flag Bit is reset.

6. Reset Signal is active for tPURST

.

Data Protection

The following circuitry has been included to prevent

inadvertent writes:

• A WREN instruction must be issued to set the Write

Enable Latch.

• CS must come HIGH at the proper clock count in order to

start a nonvolatile write cycle.

• Block Protect bits provide additional level of write

protection for the memory array.

• The WP pin LOW blocks nonvolatile write operations.

FN8126.1

12

September 16, 2005

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]