HS-3282

CLK

37

TX CLK

38

V

GND

21

SLF TST

(BD05)

S/D ENB1

(BD06)

CC

1

RCV CLK

RCVSEL

WDCNT 1

TXSEL

RCV

TIMING

TX

WLSEL

SEL

WORD GAP

SELF

TEST

S/D ENB2

(BD09)

DATA CLOCK

429D11 (A)

429D11 (B)

X1 (BD07)

Y1 (BD06)

X2 (BD10)

2

CONTROL

WORD

REGISTER

DATA S/R 1

RCV

CLK

TX

LINE

RECEIV.

ER 1

CLK

Y2 (BD11)

PARCK

(BD12)

TXSEL

(BD13)

RCVSEL

(BD14)

WLSEL

(BD15)

3

32

LATCH 1

SEL EN1

SLF

TEST

11

S/DENB

16

16

SEL 1

16

S/D

WDCNT 1

WDCNT 2

34

DECODER

CWSTR

ENTX

16

16

TX CLK

WLSEL

16

SEL 2

D

D

TX WORD

GAP

F/F

F/F

S/D CODER

33

SEL EN2

LATCH 2

32

DATA S/R 2

DATA CLOCK

429D12 (A)

429D12 (B)

4

16

16

LINE

RECEIV.

ER 2

5

16

SEL

32

31

FIFO

8 x 31

TXC

DRVR

429D0

429D0

PARITY

PARCK

SELF

TEST

11 - 20

WORD GAP

8

WLSEL

WDCNT 2

22 - 27

RCV CLK

SELF

TEST

39

6

7

9

10

28 29

30

BD15-

BD00

DATA

BUS

MR D/R1 D/R2

SEL EN1 EN2

PL1 PL2

TX/R

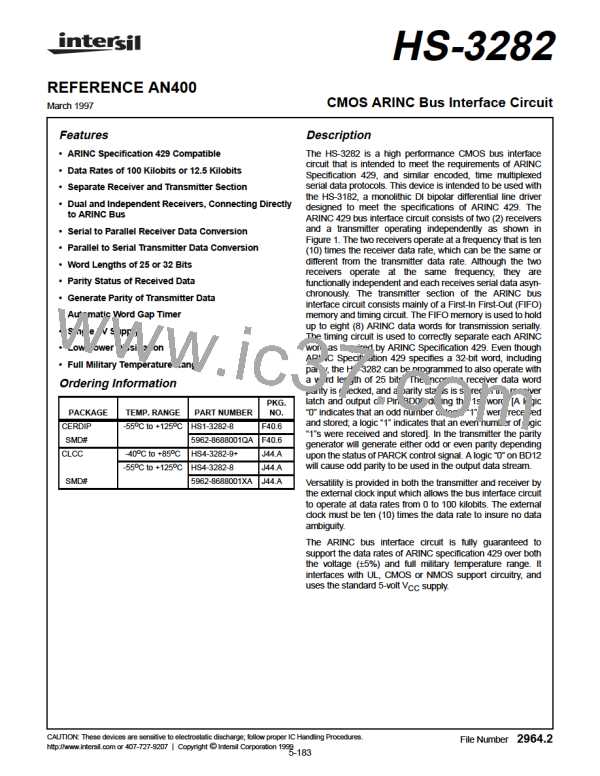

FIGURE 1. SINGLE CHIP ARINC 429 INTERFACE FUNCTIONAL BLOCK DIAGRAM

5-190

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]