HS-3282

o

o

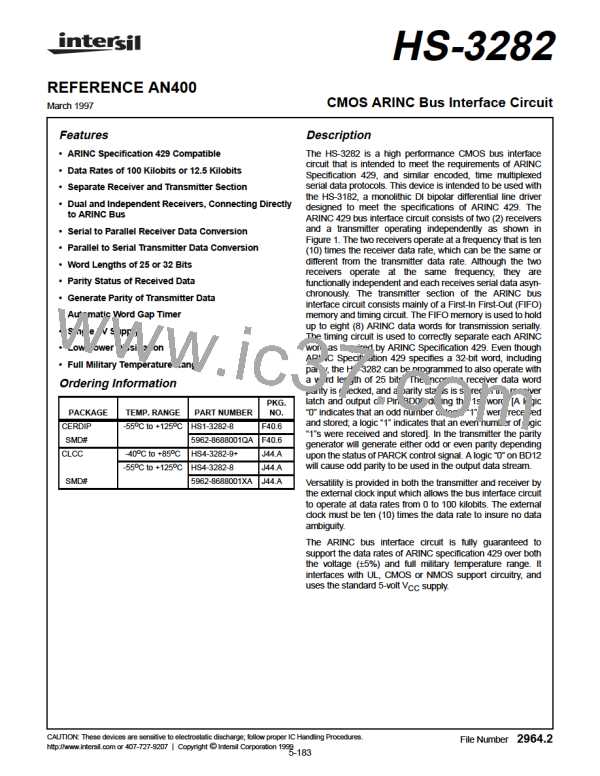

AC Electrical Performance Specifications V = 5V ±5%, T = 0 C to +70 C (HS-3282-5),

DD

A

o

o

T = -55 C to +125 C (HS-3282-8)

A

LIMITS

PARAMETER

SYMBOL

FC

CONDITIONS

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

MIN

MAX

1

UNITS

MHz

kHz

Clock Frequency

Data Rate 1/

V

V

V

V

-

DD

DD

DD

DD

FD

-

-

100

12.5

-

Data Rate 2/

FD

kHz

Master Reset Pulse Width

TMR

200

ns

RECEIVER TIMING

Receiver Ready Time From 32nd Bit 1/

Receiver Ready Time From 32nd Bit 2/

Device Ready to Enable Time

Data Enable Pulse Width

TD/R2

TD/R2

V

V

V

V

V

V

V

V

V

V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

-

-

16

µs

µs

ns

ns

ns

ns

ns

ns

ns

ns

DD

DD

DD

DD

DD

DD

DD

DD

DD

DD

128

TD/REN

TEN

0

-

200

50

-

-

-

Data Enable to Data Enable Time

Data Enable to Device Ready Reset Time

Output Data Valid to Enable Time

Data Enable to Data Select Time

Data Select to Data Enable Time

Output Data Disable Time

TENEN

TEND/R

TENDATA

TENSEL

TSELEN

TDATAEN

200

200

-

-

20

20

-

-

80

CONTROL WORD TIMING

Control Word Strobe Pulse Width

Control Word Setup Time

TCWSTR

TCWSET

TCWHLD

V

V

V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

130

130

0

-

-

-

ns

ns

ns

DD

DD

DD

Control Word Hold Time

TRANSMITTER FIFO Write Timing

Parallel Load Pulse Width

TPL

V

V

V

V

V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

200

0

-

ns

ns

ns

ns

ns

DD

DD

DD

DD

DD

Parallel Load to Parallel Load 2 Delay

Transmitter Ready Delay Time

Data Word Setup Time

TPL12

-

TTX/R

-

840

TDWSET

TDWHLD

110

0

-

-

Data Word Hold Time

TRANSMITTER Output Timing

Enable Transmit to Output Data Valid Time 1/

Enable Transmit to Output Data Valid Time 2/

Output Data Bit Time 1/

TENDAT

TENDAT

TBlT

V

V

V

V

V

V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

-

25

µs

µs

µs

µs

µs

µs

DD

DD

DD

DD

DD

DD

-

200

5.05

40.4

5.05

40.4

4.95

39.6

4.95

39.6

Output Data Bit Time 2/

TBlT

Output Data Null Time 1/

TNULL

TNULL

Output Data Null Time 2/

5-192

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]