HS-3282

o

o

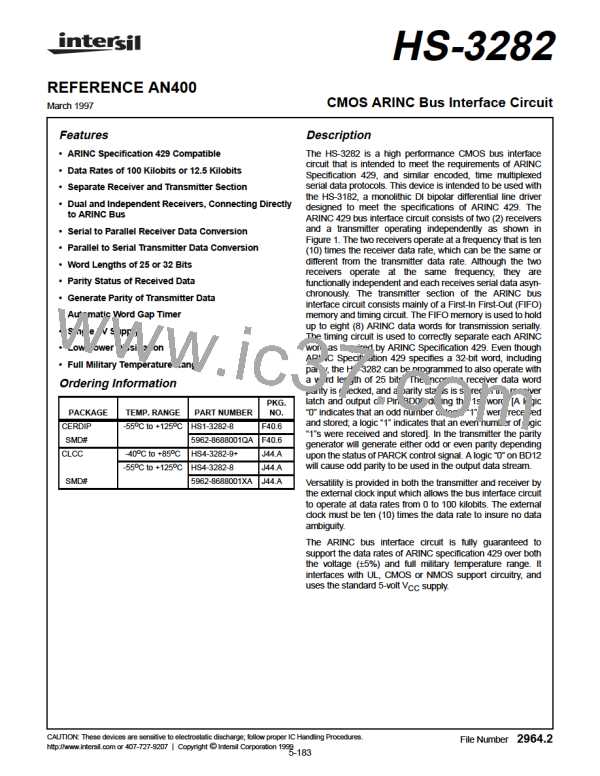

AC Electrical Performance Specifications V = 5V ±5%, T = 0 C to +70 C (HS-3282-5),

DD

A

o

o

T = -55 C to +125 C (HS-3282-8) (Continued)

A

LIMITS

PARAMETER

Data Word Gap Time 1/

SYMBOL

TGAP

CONDITIONS

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

MIN

39.6

316.8

-

MAX

40.4

323.2

400

-

UNITS

µs

V

V

V

V

DD

DD

DD

DD

Data Word Gap Time 2/

TGAP

µs

Data Transmission Word to TX/R Set Time

Enable Transmit Turnoff Time

TDTX/R

TENTX/R

ns

0

ns

REPEATER OPERATION TIMING

Data Enable to Parallel Load Delay Time

Data Enable Hold for Parallel Load Time

Enable Transmit Delay Time

TENPL

TPLEN

V

V

V

= 4.75V, 5.25V

= 4.75V, 5.25V

= 4.75V, 5.25V

0

0

0

-

-

-

ns

ns

ns

DD

DD

DD

TTX/REN

NOTES:

1. 100kHz Data Rate.

2. 12.5kHz Data Rate.

o

o

Electrical Performance Specifications V = 5V ±5%, T = 0 C to +70 C (HS-3282-5),

DD

A

o

o

T = -55 C to +125 C (HS-3282-8)

A

LIMITS

(NOTE 1)

PARAMETER

SYMBOL

CD

CONDITIONS

MIN

MAX

20

20

20

15

15

10

10

15

15

UNITS

pF

Differential Input Capacitance

V

= Open, f = 1MHz, Note 2, 3

= GND, f = 1MHz, Note 2, 3

= Open, f = 1MHz, Note 2, 3

= Open, f = 1MHz, Note 2, 4

= Open, f = 1MHz, Note 2, 5

-

-

-

-

-

-

-

-

-

DD

DD

DD

DD

DD

Input Capacitance to V

CH

V

V

V

V

pF

DD

lnput Capacitance to GND

Input Capacitance

Output Capacitance

Clock Rise Time

Clock Fall Time

CG

pF

Cl

pF

CO

pF

TLHC

THLC

TLHI

THLI

CLK = 1MHz, From 0.7V to 3.5V

CLK = 1MHz, From 3.5V to 0.7V

From 0.7V to 3.5V, Note 6

ns

ns

Input Rise Time

Input Fall Time

ns

From 3.5V to 0.7V, Note 6

ns

NOTES:

1. The parameters listed in this table are controlled via design or process parameters and are not directly tested. These parameters are

characterized upon initial design and after major process and/or design changes affecting these parameters.

2. All measurements are referenced to device GND.

3. Pins 2-3, 4-5.

4. Pins 8-10, 28, 29, 33, 34, 37, 39.

5. Pins 6, 7, 11-20, 22-27, 30-32, 38.

6. Pins 8-20, 22-29, 33, 34.

5-193

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]